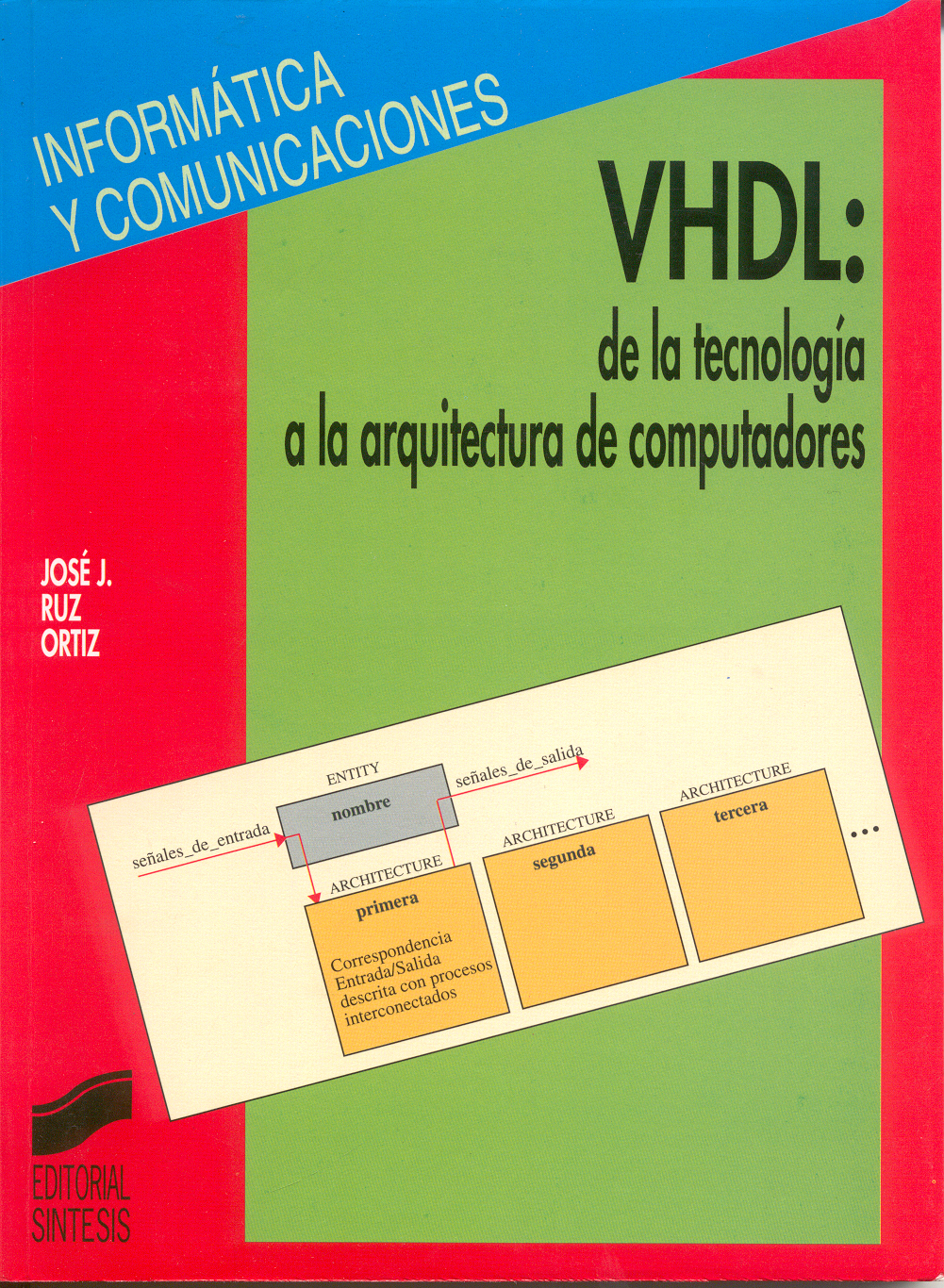

VHDL: de la Tecnología a la

Arquitectura de Computadores

José Jaime Ruz Ortiz

Departamento de Arquitectura de Computadores y Automática

Universidad Complutense de Madrid

318 Págs.

EDITORIAL SINTESIS S.A. Vallehermoso, 34. 28015 Madrid.

Depósito legal:

M.29.889-1997

ISBN:

84-7738-530-0

Con este libro

pretendemos facilitar a los estudiantes de informática y electrónica los

conocimientos básicos del lenguaje de descripción hardware VHDL para que lo

utilicen en el análisis y diseño de la estructura interna de los

computadores. Gran parte del contenido del mismo ha servido de texto guía a los

alumnos de tercer curso de Ingeniería Informática en la asignatura

Laboratorio de Estructura de Computadores, impartida por el autor

en la Escuela Superior de Informática de la Universidad Complutense de Madrid

durante los últimos cuatro años. El libro presupone en el lector

conocimientos básicos de programación, y está organizado para poner dichos

conocimientos al servicio del diseño y el modelado de dispositivos hardware.

VHDL (VHSIC Hardware

Description Language) es un lenguaje impulsado por el Departamento de

Defensa de los Estados Unidos dentro del programa VHSIC (Very High Speed

Integrated Circuits) y estandarizado por IEEE Computer Society. Con VHDL se

puede estudiar un sistema digital a diferentes niveles de abstracción dentro de

un único lenguaje de programación, acelerando considerablemente las

diferentes fases diseño y proporcionando un mejor conocimiento del mismo

cuando se aborda la fase de implementación física.

Los múltiples

intereses que han concurrido en la definición y estandarización de VHDL lo han

convertido en un lenguaje que los nuevos usuarios perciben con estructura

desordenada y difícil de aprender y utilizar. A ello ha contribuido, sin duda,

la literatura que sobre la materia se ha producido en los últimos años, muy

especialmente el propio Manual de Referencia del Lenguaje. En efecto,

muchos de los autores de libros sobre VHDL han introducido el lenguaje

desde la óptica propia de un diseñador tradicional de hardware, es decir,

comenzando con aquellas construcciones que permiten la descripción

estructural de un sistema digital. Este enfoque, que resalta la

correspondencia existente entre estas construcciones del lenguaje y la

estructura interna de los dispositivos digitales que se modelan, facilita la

comprensión superficial de algunos aspectos del lenguaje, pero dificulta el

entendimiento de la dimensión temporal del mismo, imprescindible para utilizar

adecuadamente todas sus posibilidades. Las citadas construcciones no son más

que formas sintácticamente diferenciadas de la única sentencia concurrente

disponible en el lenguaje: el proceso.

El planteamiento que

seguiremos en este libro para introducir el lenguaje es justo el inverso.

Comenzaremos con el estudio exhaustivo de las características puramente

secuenciales disponibles en VHDL para construir un proceso, análogas a las de

otros lenguajes de programación software como Pascal o Ada. Después

introduciremos el modelo temporal del lenguaje que hace posible la ejecución

concurrente y el intercambio de información entre procesos. Finalmente

analizaremos las variaciones sintácticas de los procesos que dan lugar a

las diferentes sentencias concurrentes que posibilitan la escritura de programas

con estilo estructural y de flujo de datos. Pensamos que esta organización

de los contenidos básicos del libro transmite al lector una mayor unidad del

lenguaje y proporciona los fundamentos de su semántica operacional,

imprescindible para entender el significado de las abundantes posibilidades

expresivas de VHDL.

La primera parte del

libro es una descripción básica del lenguaje compuesta de cinco capítulos. En el

capítulo 1 se introducen los conceptos básicos del lenguaje y se modelan

pequeños sistemas combinacionales y secuenciales. En el capítulo 2 se

estudian exhaustivamente las construcciones secuenciales de VHDL. En

el capítulo 3 se introduce el modelo temporal, resaltando la diferencia entre el

dominio secuencial, donde opera un funcionamiento puramente algorítmico, y el

dominio concurrente, compuesto por un conjunto de procesos que se ejecutan

asíncronamente y se comunican mediante una red de señales. En el capítulo 4 se

aborda el estudio de las sentencias concurrentes como formas particulares de

procesos escritos con una sintaxis apropiada para construir los estilos

estructural y de flujo de datos, tradicionales en los lenguajes de

descripción hardware. El capítulo 5 trata sobre las unidades de diseño

VHDL, las bibliotecas de entidades y las diferentes configuraciones que se

pueden establecer para un mismo dispositivo hardware.

En

la segunda parte del libro se aborda en tres capítulos el proceso de diseño con

VHDL. En el capítulo 6 se describen los dominios de diseño en VHDL:

comportamiento y estructural. El capítulo 7 se dedica al desarrollo de un

multiplicador binario siguiendo el algoritmo de suma y desplazamiento. Con él se

introduce el diseño de máquinas algorítmicas utilizando un ejemplo con una

sencilla interacción entre ruta de datos y controlador, lo que

facilita el uso de técnicas basadas en tipos abstractos de datos para la gestión

y depuración simbólica de las relaciones de control. Finalmente, en el capítulo

8 se aborda el diseño completo de un pequeño computador. En él se

hace uso de los conocimientos anteriores para llevar al terreno operativo los

conceptos sobre diseño y funcionamiento de un computador con arquitectura

convencional tipo von Neumann. Los programas VHDL completos de los capítulos 7 y

8 están disponibles en la dirección de Internet http://www....... .

Los directorios y nombres de archivos se indican delante de cada segmento

de código.

Con este libro hemos

pretendido, además, que el lector en general y los estudiantes de

ingeniería electrónica e ingeniería informática en particular, dispongan de una

herramienta operativa válida para otras materias relacionadas con el

hardware. Por ejemplo, como lenguaje de entrada para las herramientas de

síntesis CAD, tales como VHDL Logic Synthesis de Synopsys Inc., Autologic

de Mentor Graphics o Metamor, utilizadas en el diseño automático de circuitos

integrados. Para analizar y medir diferentes modelos de procesadores

segmentados, RISC, vectoriales, superescalares, sistólicos, VLIW- y

multiprocesadores, así como arquitecturas especificas de la aplicación. O

bien para el estudio de modelos no interpretados de análisis del

rendimiento de configuraciones de sistemas. En pocas palabras, disponer de un

lenguaje que permita llevar al terreno operativo los conocimientos del dominio

del hardware, de la misma manera que un lenguaje de propósito general

como Pascal o Modula lo hace con los conocimientos del dominio del

software.

A lo largo de todos

los capítulos hemos pretendido mantener el interés eminentemente didáctico del

libro. Por ello hemos utilizado las posibilidades expresivas de forma

libre, sin someternos a disciplinas o normalizaciones que se justifican en

ambientes profesionales y específicos dentro del mundo VHDL. Es este

el motivo de no incluir en el libro materias relacionadas con las actividades de

normalización. Tampoco hemos creído oportuno introducir las nuevas

construcciones que se derivan de la norma VHDL-92, ya que no aportan nada

significativo desde el punto de vista pedagógico.

Para finalizar quiero

agradecer la ayuda inestimable recibida de mis compañero Alvaro Ruiz-Andino y

Fernado Sáenz. La colaboración de Alvaro fue decisiva en la puesta en

marcha del Laboratorio de Estructura de Computadores de la Escuela Superior de

Informática y en el desarrollo del entorno de programación que complementó

las funciones del simulador básico de VHDL que los alumnos han venido utilizando

durante los últimos cuatro años. Fernando tuvo la paciencia de leer el borrador

del libro y colaborar con sus sugerencias y comentarios a la mejora de su

redacción.

Contenidos

Capítulo

1

Introducción

al lenguaje VHDL

1.1. Dominios de aplicación de

VHDL

1.1.1. Síntesis

automática

1.1.2. Diagnosis

de fallos

1.1.3.

Verificación formal

1.1.4. Modelado

de

rendimiento

1.1.5.

Documentación

1.2. Niveles de diseño y dominios

de

representación

1.3. Lenguajes precursores de

VHDL

1.3.1.

CDL

1.3.2.

DDL

1.3.3.

AHPL

1.3.4.

ISPS

1.3.5.

ISP'

1.3.6.

TI-HDL

1.4. Lenguajes

competidores

de

VHDL

1.4.1.

Verilog

1.4.2.

UDL/I

1.4.3.

M

1.5. Conceptos

básicos de VHDL

1.5.1. Sentencia

de asignación de variable

1.5.2. Sentencias de control del

flujo de

ejecución

1.5.2.1.

Sentencia condicional

1.5.2.2.

Sentencia alternativa

1.5.2.3.

Sentencia iterativa

1.5.2.4.

Señales

1.5.2.5. Sentencia de asignación

de

señal

1.5.2.6. Sentencia de espera

1.6. Ejemplos de

modelos VHDL

1.6.1. Puerta AND de dos

entradas

1.6.2.

Multiplexor.

1.6.3. Circuito AND con

máscara.

1.6.4. Máquina de estados

finitos.

1.6.5. Sumador

binario.

1.7.

Práctica 1

1.7.1.

Objetivos

1.7.2. Práctica

a realizar

1.7.3.

Documentación

Capítulo

2

VHDL

Secuencial

2.1. Elementos léxicos del

lenguaje

2.1.1.

Delimitadores

2.1.2.

Identificadores

2.1.3. Literales

numéricos

2.1.4. Literales

carácter

2.1.5. Cadenas

de caracteres

2.1.6. Cadenas

de bits

2.1.7. Comentarios

2.2. Objetos de

datos en VHDL

2.2.1.

Declaración de tipos

2.2.1.1. Tipo

entero

2.2.1.2. Tipo

real

2.2.1.3. Tipo

enumerado

2.2.1.4. Tipo

físico

2.2.1.5. Tipo

array

2.2.1.6. Tipo

registro

2.2.1.7. Tipo

acceso

2.2.2.

Subtipos

2.2.3.

Declaración de objetos de datos

2.2.3.1. Declaración de

variables

2.2.3.2. Declaración de

constantes

2.2.3.3.

Declaración de señales

2.2.4. Agregados

de datos

2.2.5. Atributos

de datos

2.2.5.1.

Atributos asociados a tipos o subtipos escalares

2.2.5.2.

Atributos asociados a tipos o subtipos discretos o físicos

2.2.5.3. Atributos asociados a arrays restringidos

2.3. Operadores

predefinidos y expresiones

2.4.

Alias

2.5.Sentencias

Secuenciales

2.5.1. Sentencia de asignación

de variable

(:=)

2.5.2. Sentencia

IF

2.5.3. Sentencia

Case

2.5.4. Sentencias iterativas

(LOOP,

NEXT,EXIT)

2.5.5. Sentencia

Null

2.5.6. Sentencia

Assert

2.5.7. Sentencia de asignación

de señal

(<=)

2.5.8. Sentencia

Wait

2.6.

Subprogramas

2.6.1. Definición de

subprogramas

2.6.2. Llamadas

a subprogramas

2.6.3. Valores predeterminados

en los

subprogrmas

2.7. Sobrecarga

(overloading)

2.8.

Práctica 2

2.8.1.

Objetivos

2.8.2. Prácticas

a realizar

2.8.3.

Documentación

Capítulo

3

Modelo

Temporal de VHDL

3.1 Dominios secuencial y

concurrente en VHDL

3.2 Sentencia

Process

3.3

Señales

3.3.1. Tipos de

retardo en las asignaciones de señal

3.3.2. Señales

resueltas

3.4

Simulación

3.5 Atributos de

señal

3.5.1. Atributos

de señal tipo función

3.5.2. Atributos de señal tipo

señal

3.5.3. Programa

de test de los atributos de señal

3.5.4. Programa ejemplo del uso

de atributos de

señal

3.6 Práctica

3

3.6.1.

Objetivos

3.6.2. Práctica

a realizar

3.6.3.

Documentación

Capítulo

4

Sentencias

concurrentes

4.1. Sentencia de asignación de

señal

concurrente

4.1.1. Sentencia de asignación

de señal

condicional

4.1.2. Sentencia de asignación

de señal

seleccionada

4.2. Sentencia de instanciación

de

componentes

4.2.1. Declaración de

componentes

4.2.2. Especificación de

configuración

4.2.3. Instanciación de

componentes

4.3. Sentencia de

Bloque

4.3.1. Bloques

guardados

4.3.2. Bloques

en la jerarquía de diseño

4.4. Llamada a

procedimiento concurrente

4.5. Sentencia de aserto

concurrente

4.6. Sentencia

de generación

4.7. Practica

4

4.7.1.

Objetivos

4.7.2. Práctica

a realizar

4.7.3.

Documentación

Capítulo

5

Unidades de

diseño

5.1. Declaración

de entidad

5.2. Arquitectura

de entidad

5.3.

Paquetes

5.3.1 Declaración

de paquetes

5.3.2 Cuerpo de

paquetes

5.3.3 Paquetes

estndard

5.3.3.1.

Paquete STANDARD

5.3.3.2.

Paquete TextIO

5.4. Declaración

de configuración

5.5. Bibliotecas

de diseño VHDL

5.5.1 Cláusula

library

5.5.2 Cláusula

use

5.6.

Visibilidad

5.7. Fases en la ejecución de un

programa VHDL

5.8.

Practica 5

5.8.1

Objetivos

5.8.2 Prácticas

a realizar

5.8.3

Documentación

Capítulo

6

Diseño Lógico

con VHDL

6.1. Estilos de

descripción

6.2. Modelos de descripción de

un sistema

combinacional

6.2.1. Modelo de

comportamiento

algorítmico

6.2.2. Modelo de

flujo de datos

6.2.3. Modelo

estructural

6.3. Modelos de descripción de

un circuito

secuencial

6.3.1. Modelo de

comportamiento

algorítmico

6.3.2. Modelo de

flujo de datos

6.3.3. Modelo

estructural

6.4. Modelos

estructurales de circuitos regulares

6.5. Modelos de

alta resolución: sistemas de valores lógicos

6.5.1. Sistemas de valores

lógicos en

VHDL

6.5.2. Sistema

de valores con 2 estados

6.5.3. Sistema

de valores con 3 estados

6.5.4. Sistema

de valores con 4 estados

6.5.5. Sistema

de valores con 9 estados

6.6. Practica

6

6.6.1.

Objetivos

6.6.2. Práctica

a realizar

6.6.3.

Documentación

Capítulo

7

Diseño

Algorítmico de Sistemas Digitales

7.1. Estructura de un sistema

digital

complejo

7.1.1. Ruta de

datos

7.1.2.

Controlador

7.2. Modelo de flujo de datos de

un sistema

digital

7.2.1. Modelo de

la ruta de datos

7.2.2. Modelo

del controlador

7.3.

Multiplicador binario por suma-desplazamiento

7.3.1. Algoritmo de

suma-desplazamiento

7.3.2.

Declaración de entidad

7.3.3. Codificación de un

paquete

auxiliar

7.3.4. Arquitectura de

comportamiento

funcional

7.3.5. Arquitectura de

comportamiento

algorítmica

7.3.6. Arquitectura de flujo de

datos

7.3.6.1. Ruta

de datos

7.3.6.2.

Controlador

7.3.6.3.

Conexión ruta de datos controlador

7.3.7.

Arquitectura estructural

7.3.7.1. Ruta

de datos

7.3.7.1.1 Unidades funcionales

de la ruta de

datos

7.3.7.1.2 Arquitectura

estructural de la ruta de datos

7.3.7.1.3

Paquete de tipos de control

7.3.7.2.

Controlador

7.3.7.3.

Conexión estructural Controlador-Ruta de datos

7.4. Modelado de un puerto serie

de

entrada/salida

7.5. Prácticas

7

7.5.1.

Objetivos

7.5.2.

Prácticas

7.5.3.

Documentación

Capítulo

8.

Diseño de un Computador con

VHDL

8.1. Definición

del computador

8.1.1. Memoria y

registros

8.1.2. Formato de las

instrucciones

8.1.3. Repertorio de

instrucciones

8.1.4. Ejemplos

de programas

8.2. Modelo de

comportamiento funcional

8.2.1.

Declaración de entidad

8.2.2.

Representación de las estructuras de datos

8.2.3. Ejecución

de instrucciones

8.2.4. Visualización del resultado

de la

ejecución

8.2.5. Código

VHDL del modelo completo

8.2.6. Paquete

utilidad

8.2.7. Resultados de la

simulación

8.3. Modelo

UCP-Memoria

8.3.1.

Modelo de la Memoria

8.3.2.

Modelo del reloj

8.3.3. Modelo de la Unidad

Central de

Proceso

8.3.3.1. Procedimiento de

lectura

8.3.3.2. Procedimiento de

escritura

8.3.3.3. Fases

de busqueda y decodificación-ejecución

8.3.4. Conexión

UCP-Memoria-Reloj

8.3.5. Resultados de la

simulación

8.4. Modelo

Estructural

8.4.1. Estructura de la ruta de

datos

8.4.2. Modelo estructural de la

ruta de

datos

8.4.2.1.

Multiplexor

8.4.2.2. Registros de 12 bits

(mdr, mar, pc,

ac)

8.4.2.3. Registro de

Instrucciones (ir)

8.4.2.4.

Registro de Estado

8.4.2.5.

Unidad

Aritmético-Lógica (ual)

8.4.2.6. Conexión estructural de

la ruta de

datos

8.4.3. Modelo de

la Unidad de Control

8.4.3.1. Definición de los tipos

de

control

8.4.3.2. Modelo de

comportamiento de la

Unidad de

Control

8.4.4.

Reloj

8.4.5.

Memoria

8.4.6. Conexión estructural

Reloj-Memoria-Unidad de

Control-Ruta de Datos

8.4.7. Resultados de la

simulación

8.5.Practica

8

8.5.1.

Objetivos

8.5.2. Práctica

a realizar

8.5.3.

Documentación

8.6. Práctica

9

8.6.1.

Objetivos

8.6.2. Práctica

a realizar

8.6.2.1. Arquitectura del

procesador

8.6.2.2. Conjunto de

instrucciones

8.6.2.3. Arquitectura de los

buses

8.6.3.

Documentación