## PROBLEMAS DE FUNDAMENTOS DE COMPUTADORES Hoja 5

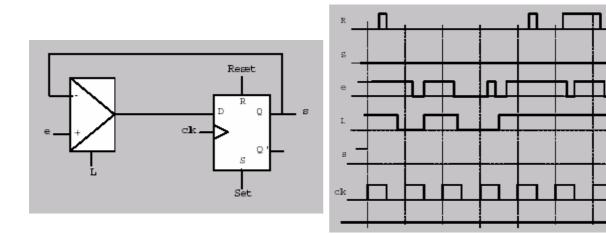

Complete el cronograma correspondiente al circuito de la figura suponiendo que inicialmente la salida Q del biestable vale 1.

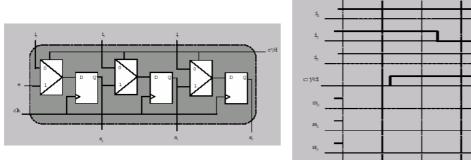

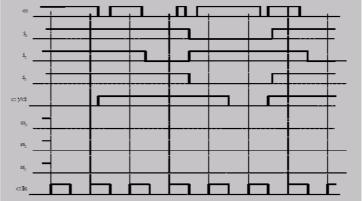

2) Complete el cronograma correspondiente al circuito de la figura suponiendo que inicialmente todas las salidas Q de los biestables valen 0.

- 3) Utilizando como bloque básico un contador módulo-16 con carga en paralelo, implemente un contador programable módulo-m (siendo 1 < m < 16). El valor máximo del contador se seleccionará mediante una entrada del sistema. Existirá además una salida de saturación que tomará el valor 1 cuando el contador alcance dicho valor máximo y además su entrada contar valga 1.

- 4) Diseñe un cronómetro con minutos, segundos y décimas de segundo mediante la utilización de contadores como los diseñados en el problema anterior. El cronómetro tendrá una entrada asíncrona (Reset) de puesta a cero. Además existirá otra entrada (Stop) tal que si toma el valor cero hace que el cronómetro se detenga hasta que Stop recupere el valor 1. Se supone que se dispone de una señal de reloj cuya frecuencia es de 100 Hz, de conversores de BCD a 7 segmentos y de visualizadores de 7 segmentos.

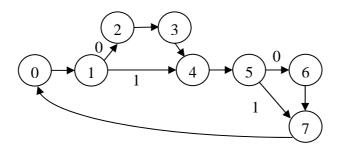

- 5) Utilizando un contador con carga en paralelo implemente un sistema secuencial que tiene una entrada X y se comporta de acuerdo con el diagrama mostrado en la figura. Además del contador, se desea usar la mínima cantidad de lógica combinacional posible.

6) Realice una implementación canónica de un sistema secuencial con una entrada X∈{0,1} y una salida Z∈{0,1}, tal que el valor de la salida será una secuencia de bits cuyo valor sea siempre igual al complemento a 2 de número formado por la secuencia de bits recibidos por la entrada. Los bits llegan por la entrada X en orden creciente de pesos. El sistema tiene otra entrada, INICIO, que funciona de la siguiente forma. Mientras que INICIO = 1 los bits recibidos por la entrada se ignoran y el sistema permanece en su estado inicial. Cuando INICIO pasa a valer 0, en cada ciclo de reloj se recibe un bit del número cuyo complemento a 2 se quiere calcular, hasta que INICIO vuelve nuevamente al valor 1. Ejemplo:

| t      | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

|--------|---|---|---|---|---|---|---|---|---|---|----|----|----|

| INICIO | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0  | 0  | 1  |

| X(t)   | Х | Х | 0 | 0 | 1 | 0 | 1 | х | 0 | 1 | 1  | 1  | х  |

| Z(t)   | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0  | 0  | 0  |

- 7) Diseñe un banco de registros formado por 4 registros de 4 bits. Si su entrada de capacitación está activada, en cada ciclo de reloj aceptará datos con destino a uno cualquiera de sus registros internos y será capaz de presentar el valor de otro cualquiera de sus registros sobre las líneas de salida de datos. Para seleccionar los dos registros que intervienen en cada ciclo de reloj el banco dispone de dos entradas de dirección. El diseño se realizará a nivel de bloques usando los módulos combinacionales y secuenciales necesarios.

- 8) Se desea diseñar un sistema secuencial con dos entradas paralelo X e Y y una salida serie Z. Por X recibe un número binario natural de 16 bits y por Y un número binario natural de 3 bits. La salida Z presenta el cociente de la división entera X / 2 , en formato serie comenzando por el bit menos significativo. Realice la implementación usando un registro de desplazamiento de 16 bits con carga en paralelo y entrada serie y los módulos combinacionales que sean necesarios.

- 9) Diseñe un contador módulo-2 con carga en paralelo y a continuación, utilizando contadores de ese tipo y las puertas lógicas necesarias, implemente un contador módulo-32 con carga en paralelo.

- 10) Realice una implementación canónica de un sistema secuencial con una entrada X∈{0,1} y una salida Z∈{0,1}, tal que el valor de la salida sea 1 siempre que hay recibido por la entrada un número par de 0 consecutivos, seguidos de dos 1s y seguidos a su vez de un número impar de bits cualesquiera. Úsense dos MUX 8 a 1 y el menor número de puertas lógicas.

- 11) Realice una implementación canónica de un sistema secuencial con una entrada  $X \in \{0,1\}$  y una salida  $Z \in \{0,1\}$ , tal que el valor de la salida sea 1 siempre que haya recibido por la entrada el patrón (0101) o el patrón (0110).

- 12) Implemente el anterior sistema con un registro de desplazamiento y puertas.

- 13) Diseñe un sistema secuencial que calcule el factorial de un número positivo de 16 bits codificado en binario puro siguiendo el siguiente algoritmo:

```

X := Xin

Y := 1;

while X > 1 do begin

Y := Y * X;

X := X - 1;

end;

Yout := Y;

```

- 14) Rediseñe el multiplicador algorítmico estudiado en teoría de manera que use, para almacenar la variable I del bucle FOR, un registro convencional en lugar de un contador. Use el sumador ya existente en el procesador para incrementar el contenido de esa variable y un nuevo módulo para detectar el fin de cuenta.

- 15) Diseñe un sistema secuencial que implemente el siguiente al algoritmo:

```

if A \ge B then C := B/4; else C := ((A + B) * 4); (en módulo 16)

```

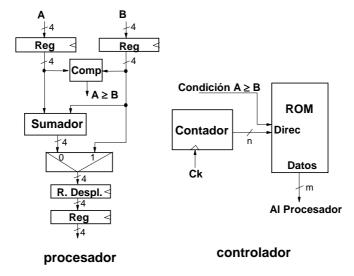

El procesador y la unidad de control se ajustarán a los esquemas mostrados en la figura. Especifique las señales de control necesarias para gobernar el procesador, obtenga el diagrama de estados de la unidad de control y determine el contenido de la ROM.