## EXAMEN PARCIAL DE FUNDAMENTOS DE COMPUTADORES

CURSO 2018-19, PRIMER PARCIAL, 1 DE JULIO DE 2019

- 1. (1 punto) Dados los siguientes números expresados en decimal: A = +3; B = -15 y C = -32.

- a) Representarlos en C2 indicando el mínimo número de bits necesario para su representación y el rango que se obtiene con ese nº de bits.

- b) Representar todos los números con 8 bits y realizar las operaciones A+B, B-C y usando aritmética en complemento a 2. En cada caso indique razonadamente si se produce desbordamiento y/o acarreo.

- c) Expresar el resultado de A+B en octal y el de B-C en hexadecimal

- 2. (2,5puntos) El sistema que acciona una bomba que lleva agua de un pozo a un depósito tiene como entrada el valor de tres sensores: A nivel mínimo del pozo, B nivel mínimo del depósito y C nivel máximo del depósito. Los tres sensores se activan cuando les cubre el agua. El sistema tiene dos salidas, ON que arranca la bomba cuando A está activada y B desactivada. OFF que para la bomba cuando A está desactivada o C está activada. Se pide:

- a) Tabla de verdad del circuito combinacional.

- b) Implementar ON con un decodificador y puertas lógicas.

- c) Implementar OFF con un multiplexor.

- **3.** (1,5 puntos) Implementar un multiplexor de prioridad que traslada a la salida el dato que se encuentra en la entrada de mayor prioridad. El sistema tendrá cuatro entradas de datos de dos bits cada una de ellas de valores comprendidos entre el 1 y el 3 y una salida de dos bits. Utilizar multiplexores, codificadores de prioridad y las puertas lógicas que sean necesarias.

- **4.** (3 puntos) Un sistema secuencial síncrono tiene una entrada, X, y una salida, Z, ambas de un bit. Inicialmente la salida vale 0, y este valor cambia a 1 sólo cuando por la entrada X se recibe el patrón '110'. Una vez recibido el citado patrón pueden plantearse dos situaciones:

- Si X=1, la salida vale 1 durante un ciclo de reloj más, volviendo tras ello al estado inicial del sistema (con independencia del valor de la entrada).

- Si X=0, la salida vale 0 durante un ciclo de reloj, volviendo tras ello al estado inicial del sistema (con independencia del valor de la entrada).

- a) Diagrama de estados de Moore (2 puntos)

- b) Implementar con una ROM (1 punto)

Implemente el sistema como máquina de Moore usando el menor número de puertas y biestables D.

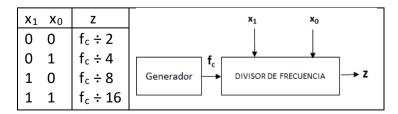

5. (2 puntos) Diseña un divisor programable de frecuencia a partir de una señal digital de frecuencia f<sub>c</sub> con factores de división 2, 4, 8 y 16. La selección del factor de división se hará con dos variables binarias x<sub>1</sub> y x<sub>0</sub>, según la siguiente tabla. Para el diseño utiliza contadores binarios de 4 bits, decodificadores y el menor número de puertas lógicas.

LOS ALUMNOS QUE SE PRESENTAN AL EXAMEN FINAL TIENEN QUE REALIZAR LOS SIGUIENTES EJERCICIOS

- EJERCICIO 1(1 PUNTO)

- EJERCICIO 3 (1,5 PUNTOS)

- EJERCICIO 4, apartado a) (2 PUNTOS)