#### **Bonus:**

### Sistema de memoria

Fundamentos de computadores II

José Manuel Mendías Cuadros

Dpto. Arquitectura de Computadores y Automática Universidad Complutense de Madrid

### Contenidos

- ✓ Introducción.

- ✓ Principio de localidad.

- ✓ Jerarquía de memoria.

- ✓ Fundamentos de memoria cache.

- ✓ Memoria cache de emplazamiento directo.

- ✓ Apéndice tecnológico.

#### Transparencias basadas en los libros:

- S.L. Harris and D. Harris. Digital Design and Computer Architecture. RISC-V Edition.

- D.A. Patterson and J.L. Hennessy. Computer Organization and Design. RISC-V Edition.

### Introducción

- Todo programador desea disponer de una memoria lo más rápida posible, del máximo tamaño y al mínimo precio.

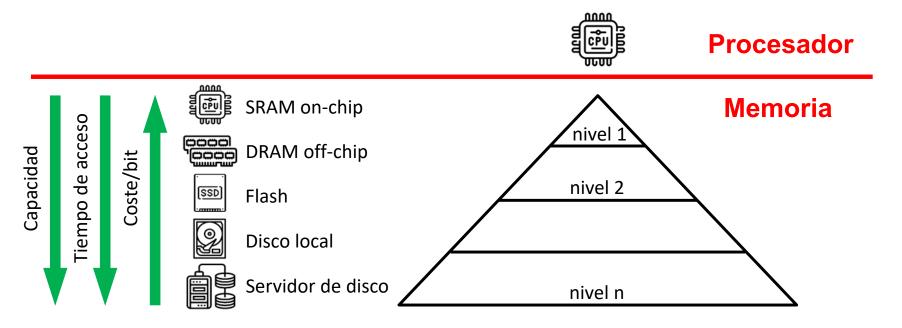

- Cada tecnología tiene sus características, pero todas cumplen que:

- o A mayor capacidad, mayor tiempo de acceso.

- A menor tiempo de acceso, mayor coste por byte.

| Tecnología                                       | Capacidad<br>típica | Tiempo de acceso<br>(ns)      | Coste<br>(\$/GiB) |

|--------------------------------------------------|---------------------|-------------------------------|-------------------|

| SRAM semiconductora                              | 10 KiB-10 MiB       | 0.5-2.5                       | 500-1000          |

| DRAM semiconductora                              | 10 GiB              | 50-70                         | 3-6               |

| Flash semiconductora<br>(Disco de estado sólido) | 100 GiB             | $5 \cdot 10^3 - 5 \cdot 10^4$ | 0.6-0.12          |

| Disco magnético                                  | 10 TiB              | $5 \cdot 10^6 - 2 \cdot 10^7$ | 0.01-0.02         |

fuente (adaptación): D.A. Patterson and J.L. Hennessy. Computer Organization and Design. RISC-V Edition (2021)

Conclusión: es imposible satisfacer al programador con una única tecnología de memoria.

### Introducción

Un sistema de memoria moderno combina de manera transparente varias tecnologías de memoria organizadas por niveles jerárquicos.

- Desde el punto de vista del procesador esta estructura, con los mecanismos de gestión apropiados, se comporta como una única memoria con:

- Tiempo de acceso medio cercano al de la tecnología más rápida (nivel 1).

- Capacidad equivalente a la disponible en la tecnología de mayor capacidad (nivel n).

- Coste/bit cercano al de la tecnología más barata (nivel n).

# Principio de localidad

### Introducción (i)

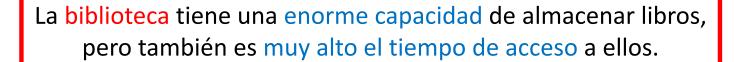

Todo estudiante aprende su carrera leyendo libros.

- Los libros de todas las carreras están en la biblioteca:

- o Para que los estudiantes puedan aprender cualquier disciplina.

## Principio de localidad

### Introducción (i)

Todo estudiante aprende su carrera leyendo libros.

Si debe ir a la biblioteca a cambiar de libro cada vez que cambia de asignatura, derrocharía mucho tiempo.

- Los libros de todas las carreras están en la biblioteca:

- Para que los estudiantes puedan aprender cualquier disciplina.

# Principio de localidad

### Introducción (i)

Todo estudiante aprende su carrera leyendo libros.

Si debe ir a la biblioteca a cambiar de libro cada vez que cambia de asignatura, derrocharía mucho tiempo.

- Los libros de todas las carreras están en la biblioteca:

- Para que los estudiantes puedan aprender cualquier disciplina.

# Principio de localidad

Introducción (ii)

Para reducir este tiempo, acerca los libros que más usa.

# Principio de localidad

#### Introducción (ii)

Para reducir este tiempo, acerca los libros que más usa.

- Coloca libros del curso sobre la mesa de estudio:

- Para tenerlos cerca cuando cambia de asignatura.

- Caben pocos libros, pero es muy rápido acceder a ellos.

#### ق نة FC-2

# Principio de localidad

#### Introducción (ii)

Para reducir este tiempo, acerca los libros que más usa.

- Coloca libros del curso sobre la mesa de estudio:

- Para tenerlos cerca cuando cambia de asignatura.

- Caben pocos libros, pero es muy rápido acceder a ellos.

- Coloca los libros del resto de la carrera en una librería:

- Ordenados por curso por si hay algo que repasar.

- Su capacidad es intermedia y el tiempo de acceso a la librería es mayor que al escritorio pero menor a la biblioteca.

Solo irá a la biblioteca cuando necesite un libro distinto.

## Principio de localidad

#### Introducción (iii)

o Los que se usarán con mayor probabilidad están más cerca.

- Funciona porque los libros leídos no son aleatorios:

- o En cada momento, solo necesita un pequeño conjunto de los libros de la biblioteca.

- o Típicamente alterna la lectura de libros del mismo curso.

- Ocasionalmente se leen libros de cursos pasados o de temáticas afines.

Los libros leídos por un estudiante tienen:

- Localidad temporal: si hoy lee un libro, es muy probable que en próximos días lea el mismo.

- Localidad espacial: Si hoy lee un libro, es muy probable que en próximos días lea uno situado cerca.

- Ya que los libros de la misma temática suelen colocarse juntos.

# Principio de localidad

### Introducción (iv)

- El principio de localidad es universal y se usa en infinidad de campos de la informática para mejorar el rendimiento, lo aplican:

- o Los programadores en ensamblador al decidir las variables que almacena en los registros del procesador, evitando el retraso del acceso a memoria.

- Los navegadores Web al conservar copias locales de las páginas recientemente visitadas, evitando el retraso de la descarga.

- Los servidores de Bases de Datos al conservar copias del resultado de las consultas más recurrentes, evitando el retraso de la consulta.

- Los usuarios finales al decidir las aplicaciones que instala, al organizar sus documentos, al hacer backups de sus archivos, etc..

- En particular el principio de localidad se usa para gestionar la jerarquía de memoria de un computador moderno.

# Principio de localidad

#### Localidad de referencias

- En todo intervalo de tiempo, un procesador solo usa un pequeño conjunto de los datos/instrucciones del programa.

- Las referencias a memoria que hace no son aleatorias ya que tienen:

- Localidad temporal: si direcciona un dato/instrucción es muy probable que en el futuro próximo direccione el mismo.

- Los programas tienen bucles que ejecutan varias veces las mismas instrucciones.

- Los programas se estructuran en funciones que se ejecutan recurrentemente.

- Las variables almacenadas en memoria son leídas/escritas recurrentemente.

- Localidad espacial: si direcciona un dato/instrucción es muy probable que en el futuro próximo direccione los ubicados en direcciones próximas.

- Las instrucciones de un programa se ubican en direcciones consecutivas y se ejecutan normalmente en secuencia.

- Las variables locales a una función se ubican en direcciones consecutivas del marco de pila y se alterna la lectura/escritura de todas ellas.

- Los arrays se ubican en direcciones consecutivas y, además es común procesar sus elementos secuencialmente.

### Jerarquía de memoria

#### Principios de funcionamiento

- El objetivo de un sistema jerárquico de memoria es:

- Asegurar que las referencias (datos/instrucciones) que en todo momento necesita el procesador estén en el nivel más alto de jerarquía.

- Lo consigue haciendo uso del principio de localidad:

- Manteniendo en cada nivel una copia de un subconjunto de las referencias almacenadas en el nivel inmediatamente inferior.

- Manteniendo cerca del procesador las últimas referencias solicitadas.

- Moviendo cerca del procesador no sólo la referencia solicitada sino también sus contiguas.

# Jerarquía de memoria

### Ejemplo

- La jerarquía de memoria de un computador típico tiene muchos niveles

- Que pueden ser más si los discos incorporan sus propias caches para acelerar el tiempo medio de acceso a sus datos.

| Nivel             | Ubicación     | Tecnología     | Tiempo<br>de acceso | Capacidad | Gestionado<br>por |

|-------------------|---------------|----------------|---------------------|-----------|-------------------|

| Registros         | Ruta de datos | flip-flop CMOS | 1 ciclo             | 1 KiB     | Compilador        |

| Cache nivel 1     | On-chip       | SRAM           | 2-4 ciclos          | 64 KiB    | Hardware          |

| Cache nivel 2     | On-chip       | SRAM           | 10 ciclos           | 256 KiB   | Hardware          |

| Cache nivel 3     | On-chip       | SRAM           | 40 ciclos           | 16 MiB    | Hardware          |

| Memoria principal | Off-chip      | DRAM           | 200 ciclos          | 16 GiB    | SO                |

| Disco Flash       | Periférico    | Flash          | ~µs                 | 512 GiB   | SO                |

| Disco duro        | Periférico    | Magnética      | ~ms                 | 2 TiB     | SO                |

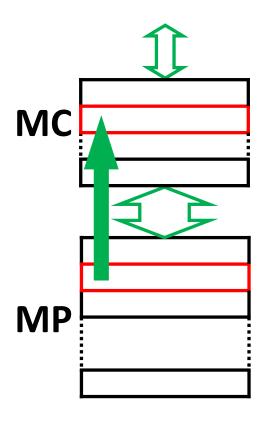

## Fundamentos de memoria cache

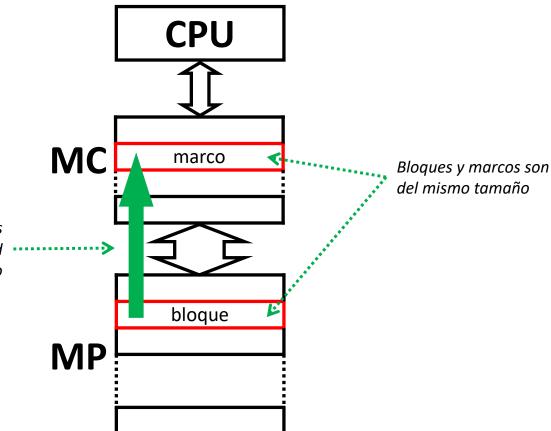

- Analicemos una jerarquía de memoria elemental de 2 niveles:

- o Formada por una memoria cache (MC) y una memoria principal (MP).

- La MC es una memoria pequeña y rápida cuyo objetivo reducir el tiempo medio de acceso a los datos/instrucciones almacenados en MP.

La MC contiene copia de los datos/instrucciones contenidas en MP que con mayor probabilidad serán direccionados en un futuro próximo

### Fundamentos de memoria cache

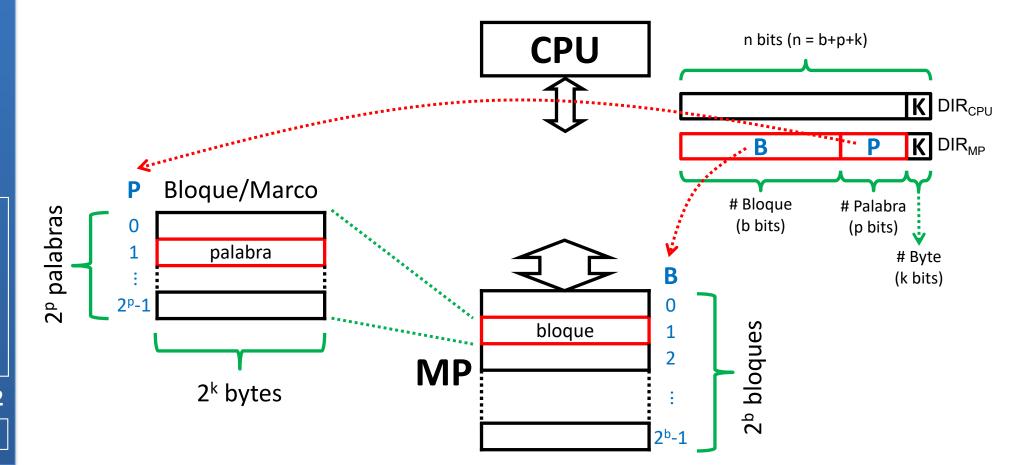

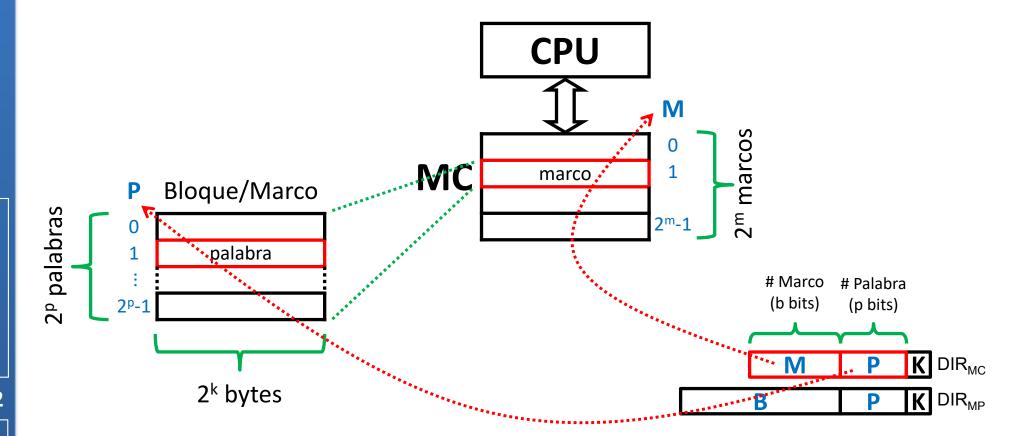

#### Organización

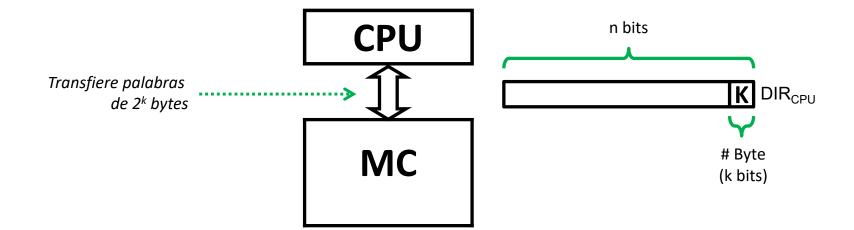

- Para el procesador la memoria cache es transparente:

- El procesador envía direcciones de n bits.

- o Por cada dirección, la MC transfiere la palabra de 2<sup>k</sup> bytes correspondiente.

### Fundamentos de memoria cache

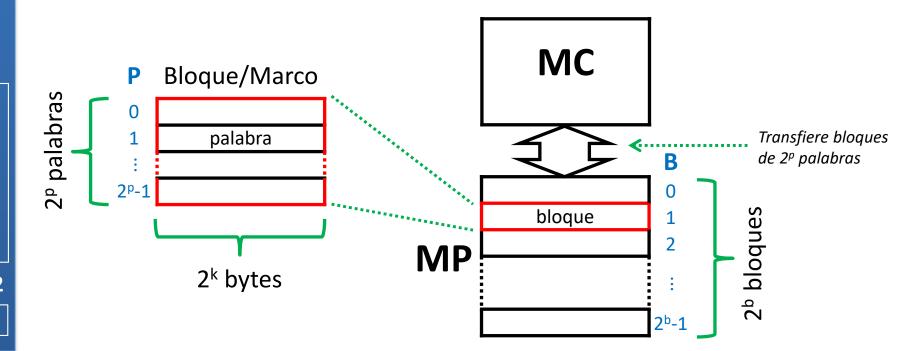

### Organización de memoria principal (i)

- La memoria principal (direccionable por bytes):

- Tiene capacidad para 2<sup>n-k</sup> palabras de 2<sup>k</sup> bytes cada una (2<sup>n</sup> bytes).

- Está "dividida" en nB = 2<sup>b</sup> bloques de tamaño fijo de 2<sup>p</sup> palabras por bloque.

- Por cada dirección, la MP transfiere a la MC un bloque al completo.

- El bloque contiene la palabra direccionada y sus contiguas (localidad espacial).

### Fundamentos de memoria cache

### Organización de memoria principal (ii)

- Existe una relación inmediata entre la dirección de la palabra y:

- El número de bloque de MP que la contiene y que es transferido a MC.

- Su posición relativa dentro del bloque.

### Fundamentos de memoria cache

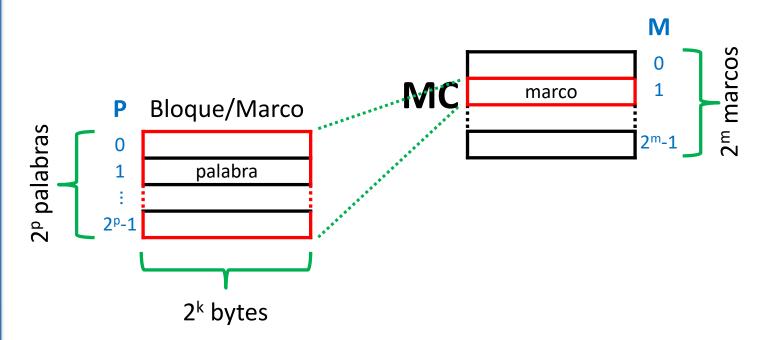

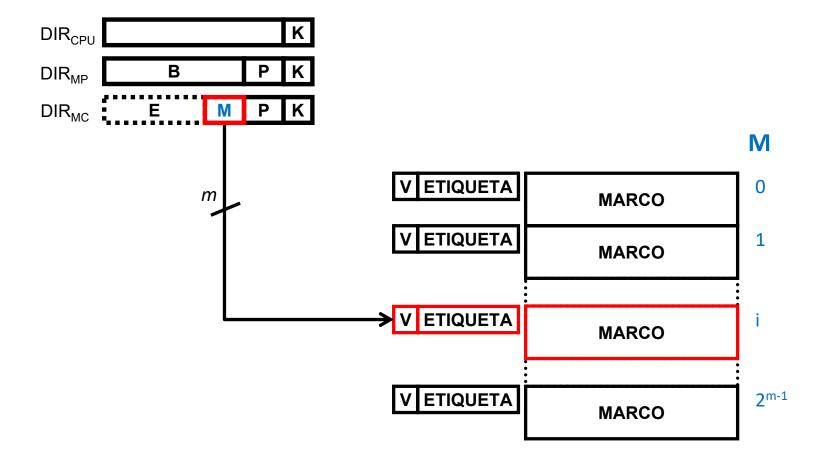

Organización de memoria cache (i)

#### La memoria cache:

- Está "dividida" en nM = 2<sup>m</sup> marcos de bloque (líneas de cache) de tamaño fijo de 2<sup>p</sup> palabras por marco (nM << nB).

- Tiene capacidad para  $2^{m+p}$  palabras de  $2^k$  bytes cada una  $(2^{m+p+k}$  bytes).

- Cada marco almacena un bloque distinto de MP.

- Y lo conserva hasta que sea reemplazado por otro (localidad temporal).

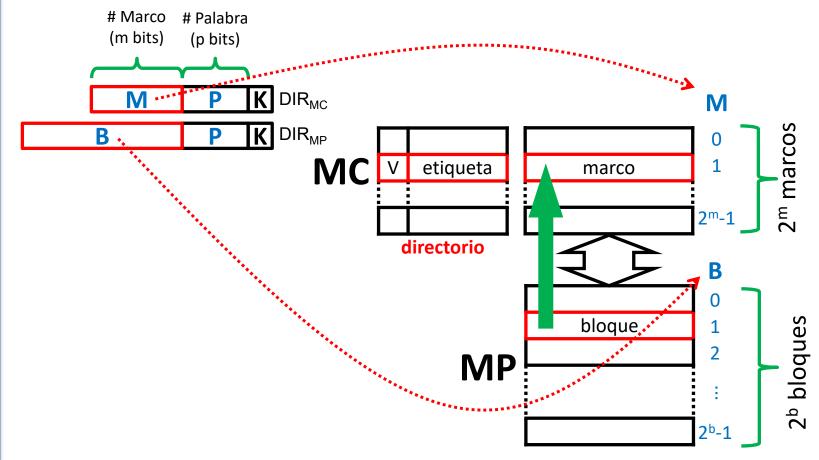

### Fundamentos de memoria cache

### Organización de memoria cache (ii)

- Además, la MC dispone de un directorio en el que, cada marco, tiene:

- O Una etiqueta indicando el número de bloque de MP del que tiene copia.

- o Un bit de validez indicando si contiene o no un bloque válido.

- Inicialmente vale 0, cuando el marco se rellena se pone a 1

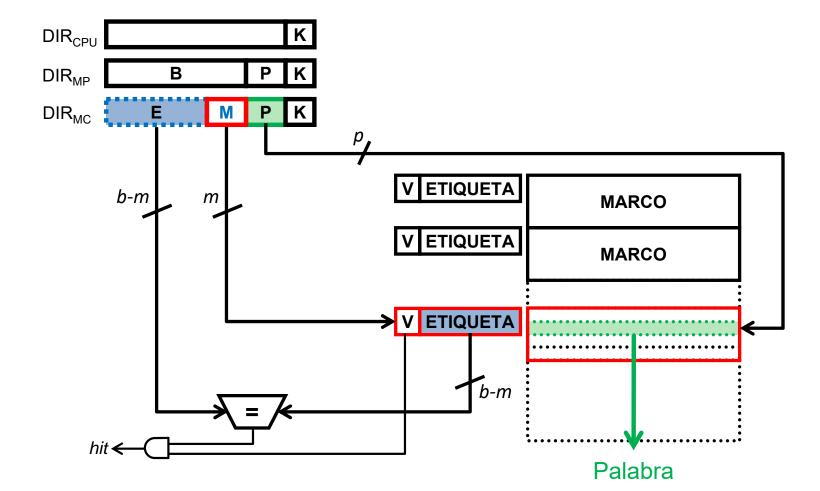

### Organización de memoria cache (iii)

Conocido el marco en donde se ubica cada bloque, la obtención de la posición relativa de la palabra dentro del marco es inmediata.

### Fundamentos de memoria cache

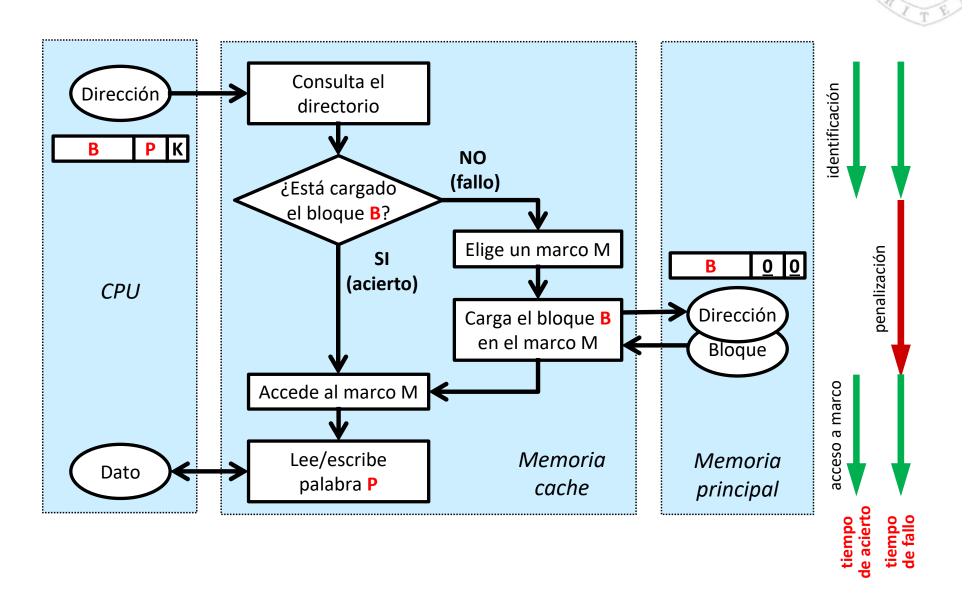

Ciclo de acceso

### Caracterización (i)

- Toda referencia (dato/instrucción) generada por la CPU puede ser un:

- Acierto (hit): la referencia solicitada está en MC.

- Tasa de aciertos (hit ratio, H): fracción de referencias encontradas en MC,  $H=\frac{n_h}{n}$

- Tiempo de acierto (t<sub>h</sub>): tiempo identificación + tiempo de acceso a MC.

- Fallo (miss): la referencia solicitada no está en MC y hay que cargar de MP el bloque que lo contiene.

- Tasa de fallos (miss ratio, F):  $F = \frac{n_m}{n} = \frac{(n n_h)}{n} = 1 H$

- Tiempo de fallo: tiempo de acierto + tiempo de penalización

- Tiempo de penalización (t<sub>p</sub>): tiempo de reemplazamiento de un bloque cargado en MC por el de MP que contiene la referencia solicitada.

- El tiempo medio de acceso a MC (T<sub>MAM</sub>):

$$t_{MAM} = \frac{n_h}{n} \cdot t_h + \frac{n_m}{n} \cdot (t_h + t_p) = H \cdot t_h + (1 - H) \cdot (t_h + t_p)$$

$$t_{MAM} = t_h + (1 - H)t_p$$

Caracterización (ii)

- MP y MC están implementadas con tecnologías diferentes

- o MP utiliza DRAM y MC utiliza SRAM.

- Cada una con su Capacidad (S), Coste por byte (C) y Tiempo de acceso (T).

- El par MC+MP en conjunto estará caracterizado por:

$$T = T_{MAM} = t_h + (1 - H)t_p$$

$si \begin{cases} H \approx 1 \\ t_h \approx T_{SRAM} \end{cases} \Rightarrow T \approx T_{SRAM}$

Tiempo de acceso cercano al de la memoria con tecnología más rápida (MC)

### Fundamentos de memoria cache

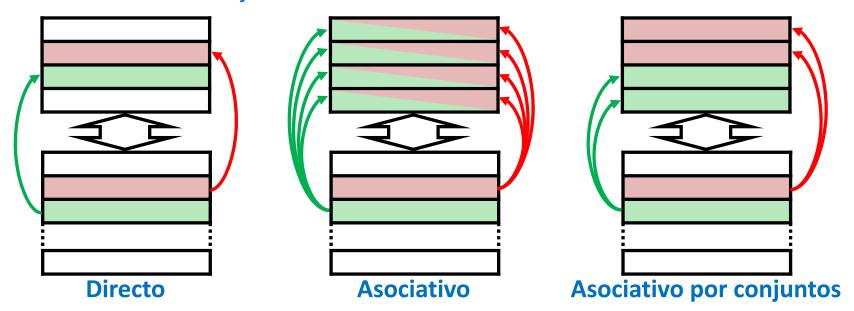

#### Aspectos básicos de diseño (i)

- Política de emplazamiento: determina en qué marcos de MC puede cargarse cada bloque de MP.

- Necesaria porque existen menos marcos en MC que bloques en MP.

- Tipos:

- Directo: cada bloque solo puede cargarse en un único marco.

- Asociativo: cada bloque puede cargarse en cualquier marco.

- Asociativo por conjuntos: cada bloque puede cargarse en cualquiera de los marcos de un conjunto determinado de marcos.

Aspectos básicos de diseño (ii)

- Política de reemplazamiento: determina qué bloque cargado sustituir cuando están ocupados todos los marcos en donde puede cargarse.

- O Necesaria si un bloque puede cargarse en más de un marco.

- No aplica a MC de emplazamiento directo.

- Tipos:

- Aleatorio: reemplaza un bloque escogido al azar.

- FIFO (first in first out): reemplaza el bloque que lleve más tiempo cargado.

- LRU (least recently used): reemplaza el que lleve más tiempo sin referenciase.

FC-2

Aspectos básicos de diseño (iii)

- Cuando la CPU escribe un dato, éste se almacena en la MC.

- Si hay acierto, se escribe en el bloque cargado que corresponda.

- Si hay fallo, se carga en MC el nuevo bloque y se realiza la escritura.

- Política de actualización: determina cuándo se actualiza en MP un bloque modificado en MC.

- Necesaria para mantener la coherencia entre la MC y la MP.

- Tipos:

- Escritura inmediata (write-through): la MP se actualiza a la vez que se escribe en el bloque cargado en MC.

- Post-escritura (write-back): la MP sólo se actualiza cuando se reemplaza el bloque modificado.

Aspectos básicos de diseño (iv)

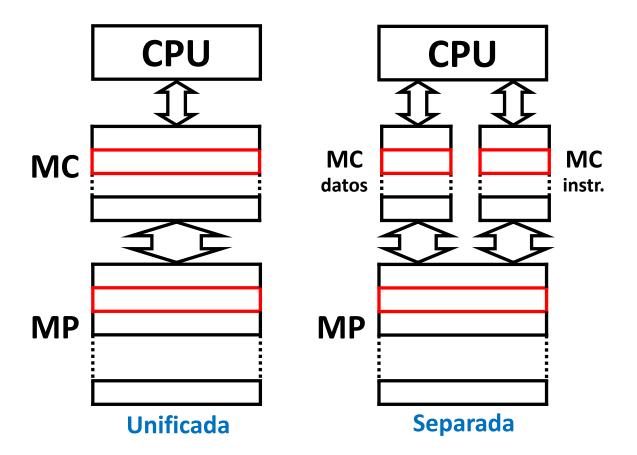

- Cache unificada: existe una única MC común para datos e instrucciones.

- Cache separada: existen dos MC una para datos y otra para instrucciones.

- Cada una puede implementarse con políticas diferentes.

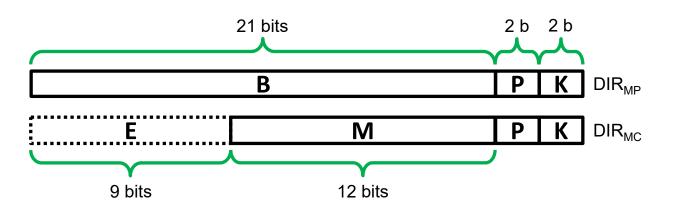

# MC de emplazamiento directo

#### Organización (i)

- Un bloque B se carga siempre en el marco M = B mod nM

- Como nM = 2<sup>m</sup> entonces M = "m bits menos significativos de B"

- El acceso al marco y al directorio es directo y se realiza en paralelo.

# MC de emplazamiento directo

### Organización (ii)

- Para cada marco, el directorio almacena una etiqueta con los b-m bits restantes de la dirección del bloque almacenado.

- Basta comparar las etiquetas para saber si un bloque está cargado en MC.

# MC de emplazamiento directo

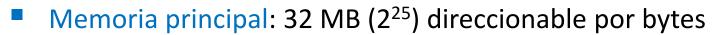

#### Ejemplo de dimensionamiento

Tamaño de palabra: 4 B

Tamaño de bloque: 16 B (4 palabras)

Memoria cache de emplazamiento directo: 64 KB

• Número de bloques en MP (nB) = 32 MB / 16 B = 2 M ( $2^{21}$ )

Número de marcos en MC (nM) = 64 KB / 16 B = 4 K (2<sup>12</sup>)

Anchura de etiqueta = 21 – 12 = 9

## MC de emplazamiento directo

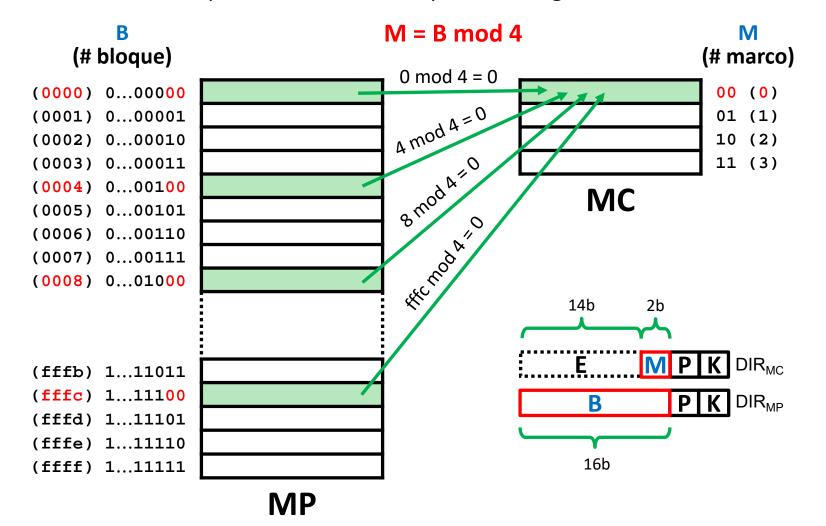

#### Ejemplo de emplazamiento (i)

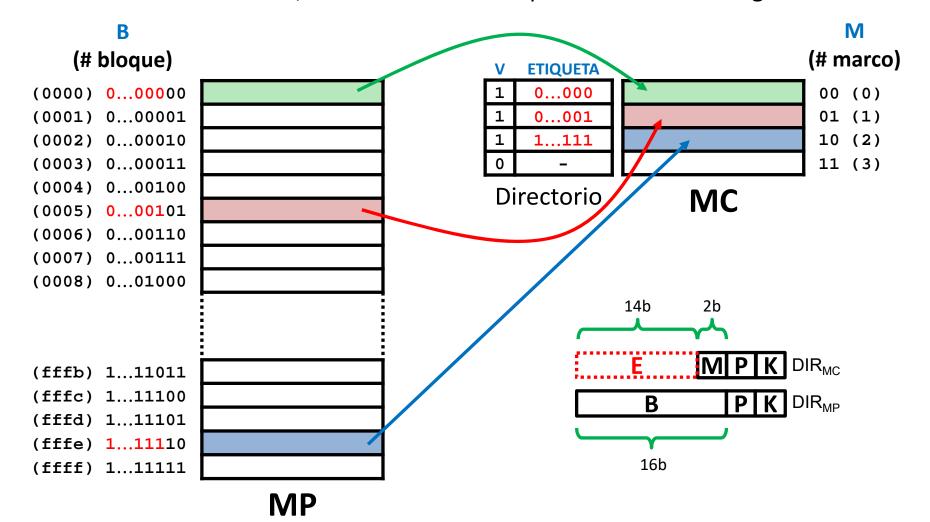

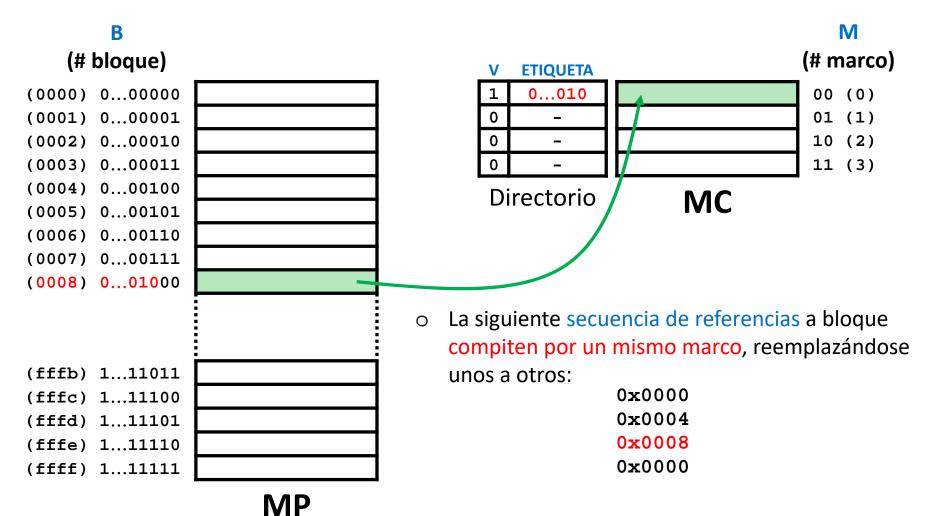

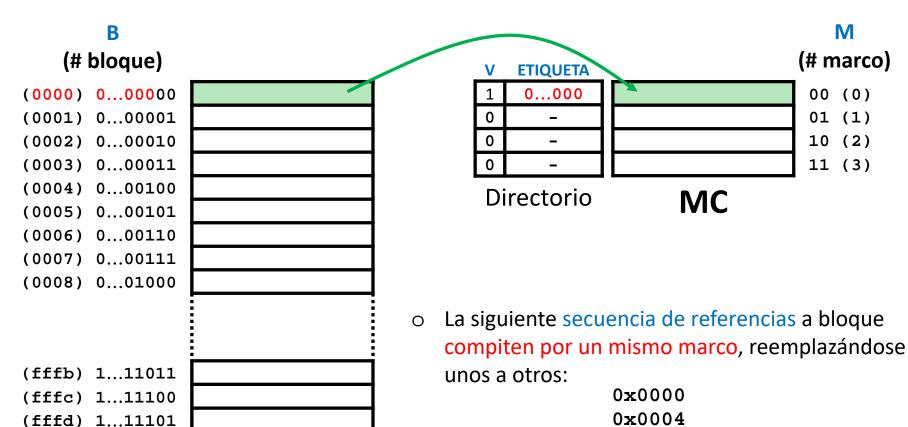

- Emplazamiento directo de una MP 2<sup>16</sup> bloques en una MC de 4 marcos

- $\circ$  2<sup>16</sup>÷4 = 2<sup>14</sup> bloques de MP distintos pueden cargarse en el mismo marco MC

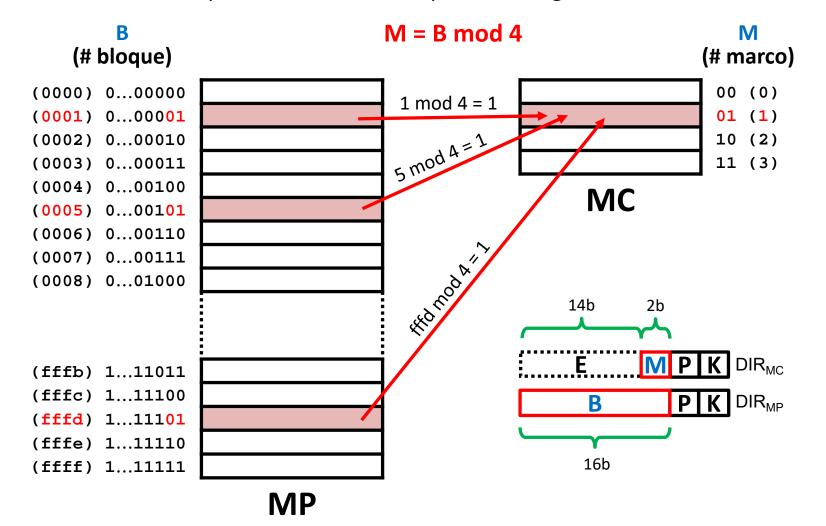

# MC de emplazamiento directo

Ejemplo de emplazamiento (ii)

- Emplazamiento directo de una MP 2<sup>16</sup> bloques en una MC de 4 marcos

- $\circ$  2<sup>16</sup>÷4 = 2<sup>14</sup> bloques de MP distintos pueden cargarse en el mismo marco MC

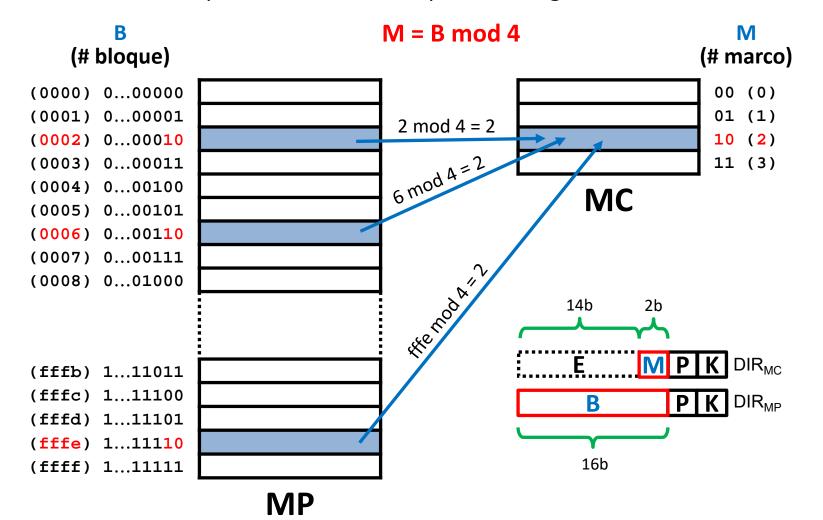

# MC de emplazamiento directo

Ejemplo de emplazamiento (iii)

- Emplazamiento directo de una MP 2<sup>16</sup> bloques en una MC de 4 marcos

- $\circ$  2<sup>16</sup>÷4 = 2<sup>14</sup> bloques de MP distintos pueden cargarse en el mismo marco MC

# MC de emplazamiento directo

Ejemplo de emplazamiento (iv)

- Emplazamiento directo de una MP 2<sup>16</sup> bloques en una MC de 4 marcos

- o En todo momento, un máximo de 4 bloques de MP están cargados en MC

## MC de emplazamiento directo

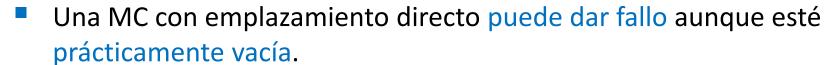

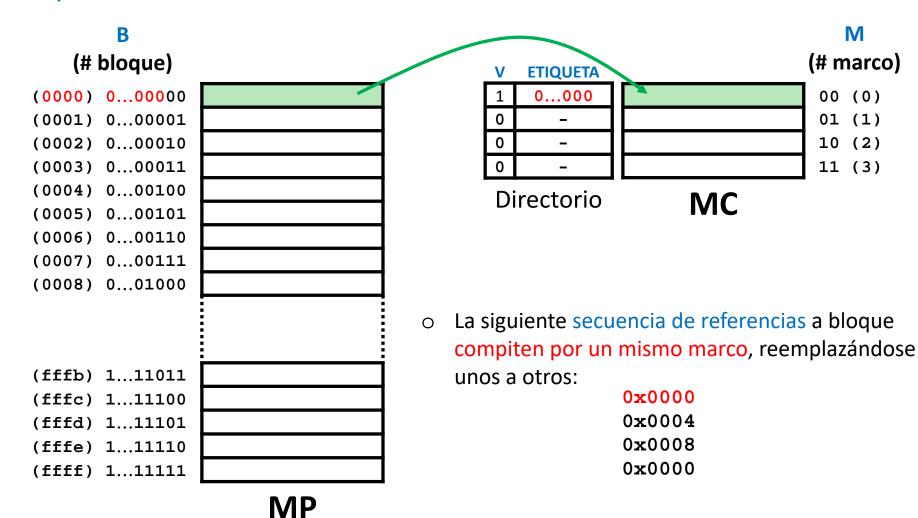

Ejemplo de fallos por conflicto (i)

| (#     | B<br>bloque) |  |

|--------|--------------|--|

| (0000) | 000000       |  |

| (0001) | 000001       |  |

| (0002) | 000010       |  |

| (0003) | 000011       |  |

| (0004) | 000100       |  |

| (0005) | 000101       |  |

| (0006) | 000110       |  |

| (0007) | 000111       |  |

| (0008) | 001000       |  |

|        |              |  |

| (fffb) | 111011       |  |

| (fffc) | 111100       |  |

| (fffd) | 111101       |  |

| (fffe) | 111110       |  |

| (ffff) | 111111       |  |

|            | V | ETIQUETA |    | (# marco) |

|------------|---|----------|----|-----------|

|            | 0 | -        |    | 00 (0)    |

|            | 0 | -        |    | 01 (1)    |

|            | 0 | -        |    | 10 (2)    |

|            | 0 | -        |    | 11 (3)    |

| Directorio |   | rectorio | MC | -         |

M

La siguiente secuencia de referencias a bloque compiten por un mismo marco, reemplazándose unos a otros:

> 0x0000 0x0004 0x0008 0x0000

# Sistema de memoria

#### FC-2

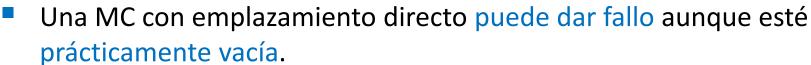

## MC de emplazamiento directo

#### Ejemplo de fallos por conflicto (ii)

M

(ffff) 1...11111

## MC de emplazamiento directo

Ejemplo de fallos por conflicto (iii)

|        | В       |          |   |    |

|--------|---------|----------|---|----|

| (#     | bloque) |          |   |    |

| (0000) | 000000  |          |   |    |

| (0001) | 000001  |          |   |    |

| (0002) | 000010  |          |   |    |

| (0003) | 000011  |          |   |    |

| (0004) | 000100  |          |   |    |

| (0005) | 000101  |          |   |    |

| (0006) | 000110  |          |   |    |

| (0007) | 000111  |          |   |    |

| (8000) | 001000  |          |   |    |

|        |         |          |   |    |

|        |         | •        | 0 | La |

|        |         | <u> </u> |   | CO |

| (fffb) | 111011  |          |   | un |

| (fffc) | 111100  |          |   |    |

| (fffd) | 111101  |          |   |    |

| (fffe) | 111110  |          |   |    |

|        |         |          |   |    |

| _ | V          | ETIQUETA |    | (# marco) |

|---|------------|----------|----|-----------|

|   | 1          | 0001     | 4  | 00 (0)    |

|   | 0          | -        |    | 01 (1)    |

|   | 0          | -        |    | 10 (2)    |

|   | 0          | -        |    | 11 (3)    |

| _ | Directorio |          | MC | -         |

La siguiente secuencia de referencias a bloque compiten por un mismo marco, reemplazándose unos a otros:

0x0000 0x0004 0x0008 0x0000

MP

## MC de emplazamiento directo

Ejemplo de fallos por conflicto (iv)

(fffe) 1...11110

(ffff) 1...11111

## MC de emplazamiento directo

#### Fallos por conflicto

0x0008

$0 \times 0000$

## MC de emplazamiento directo

#### **Conclusiones**

- La MC con emplazamiento directo tiene numerosas ventajas:

- Tiempos bajos de identificación, de acceso y de elección de marco.

- Todo bloque tiene un marco único en donde puede cargarse.

- El acceso al marco y al directorio es directo a partir de la dirección recibida.

- Se requiere una única comparación para saber si el bloque está cargado.

- Bajo coste hardware.

- El directorio solo almacena parte de la dirección del bloque.

- La identificación requiere un único comparador.

- Sin embargo, tiene una desventaja importante:

- Alta probabilidad de fallos por conflicto.

- Puede haber reemplazamientos aún estando la MC prácticamente vacía.

- Suele tener una tasa de fallos superior a otras políticas.

43

- Celdas elementales de memoria RAM.

- Memoria SRAM asíncrona.

- Memoria DRAM asíncrona.

- Memoria DRAM síncrona.

- Módulos de memoria DRAM síncrona.

- Controlador de memoria.

Apéndice tecnológico

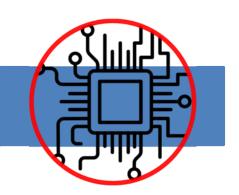

#### Celdas elementales en memorias RAM

- Las celdas de RAM se clasifican por:

- o El número de transistores usados en su implementación.

- o Por la tecnología usada para almacenar 1 bit de información.

FC-2

por necesitar +20T

No se usan flip-flops

Las celdas de SRAM almacenan el bit en un lazo de realimentación Las celdas de DRAM almacenan el bit como el nivel de carga de un condensador

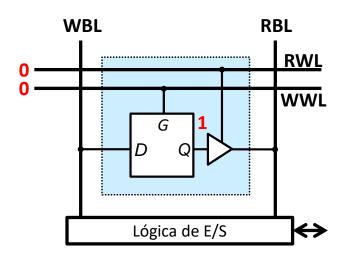

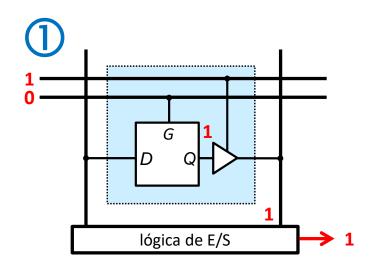

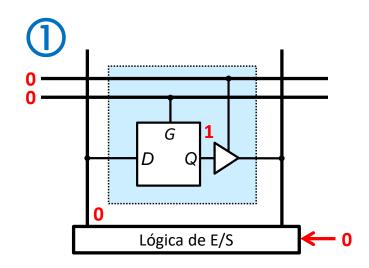

Celda SRAM 12T: lectura

- Se activa RWL:

- La celda propaga el valor almacenado por RBL.

- La celda sigue conservando el valor almacenado.

- La operación finaliza desactivando RWL.

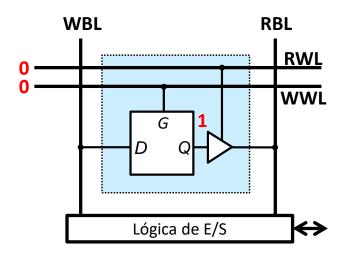

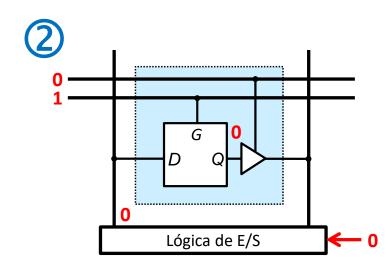

Celda SRAM 12T: escritura

- Se pone en WBL el valor a almacenar.

- Se activa WWL:

- o La celda carga el valor a almacenar.

- o Esta es una operación rápida.

- La operación finaliza desactivando WWL.

FC-2

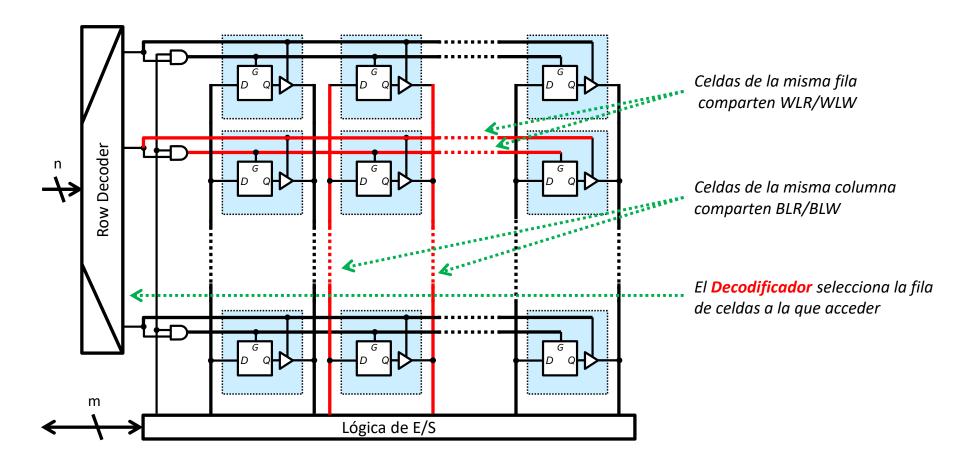

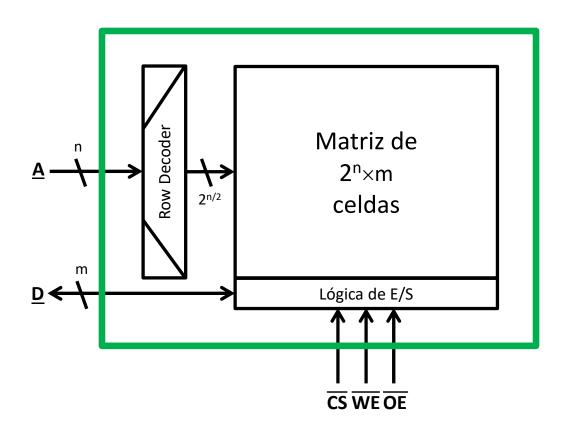

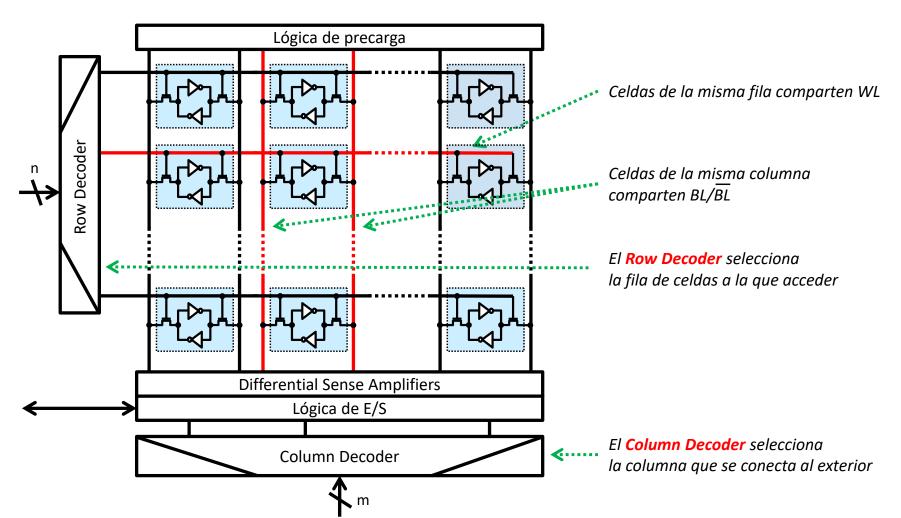

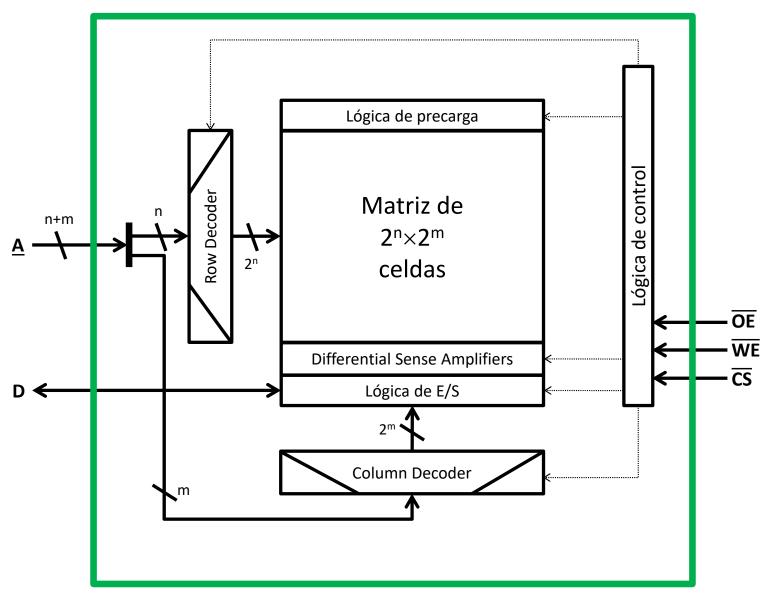

#### Memoria SRAM (12T) asíncrona: matriz de celdas

- Las celdas se distribuyen en una matriz 2<sup>n</sup>×m (con 2<sup>n</sup>>>m) con:

- Tantas filas como palabras tenga la memoria.

- Tantas columnas como anchura tenga la palabra.

Memoria SRAM (12T) asíncrona: estructura

## Aspectos tecnológicos

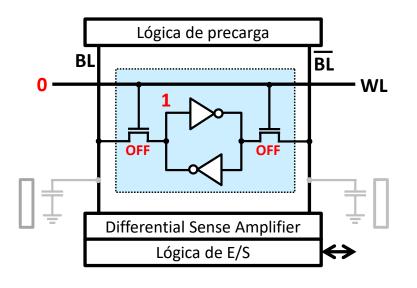

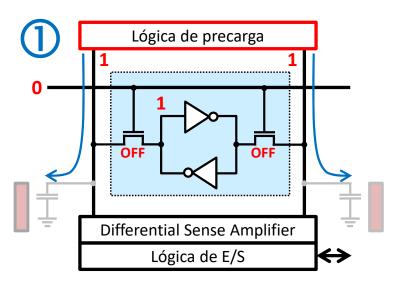

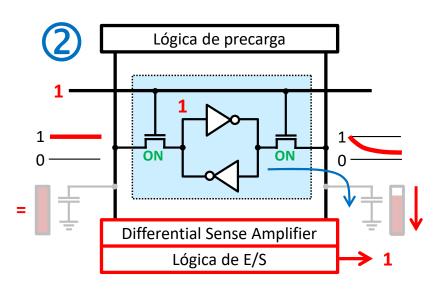

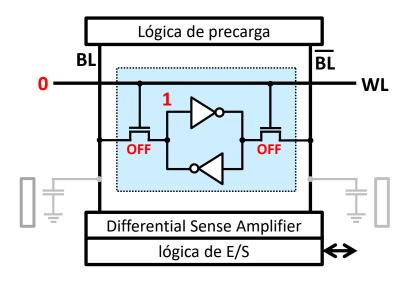

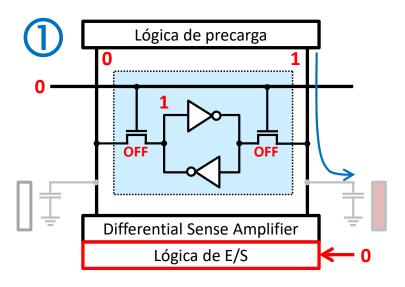

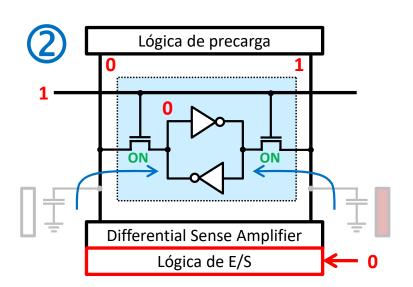

#### Celda SRAM 6T: lectura

- 1. Se precargan a Vdd las BL.

- 2. Se activan WL y sense amplifier:

- La celda propaga los valores que almacena por las BLs.

- La celda conserva el valor almacenado.

- Se amplifica la pequeña diferencia de voltaje entre BLs

- Se transfiere al exterior el valor leído.

- Se desactivan WL y sense amplifier.

## bonus:

#### FC-2

## Aspectos tecnológicos

Celda SRAM 6T: escritura

- 1. El valor a almacenar se pone en BL e invertido en BL.

- 2. Se activa WL:

- La celda carga el valor a almacenar.

- Se desactiva WL.

## Aspectos tecnológicos

#### Memoria SRAM (6T) asíncrona: matriz de celdas

- Las celdas se distribuyen en una matriz 2<sup>n</sup>×2<sup>m</sup> (con n≈m)

- El decodificador se divide en 2 para reducir sustancialmente su coste.

Memoria SRAM (6T) asíncrona: organización (i)

### Aspectos tecnológicos

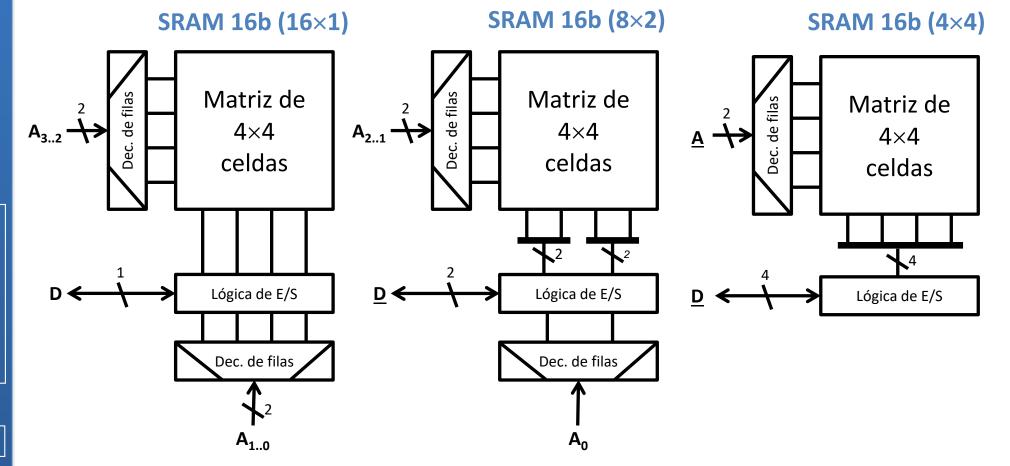

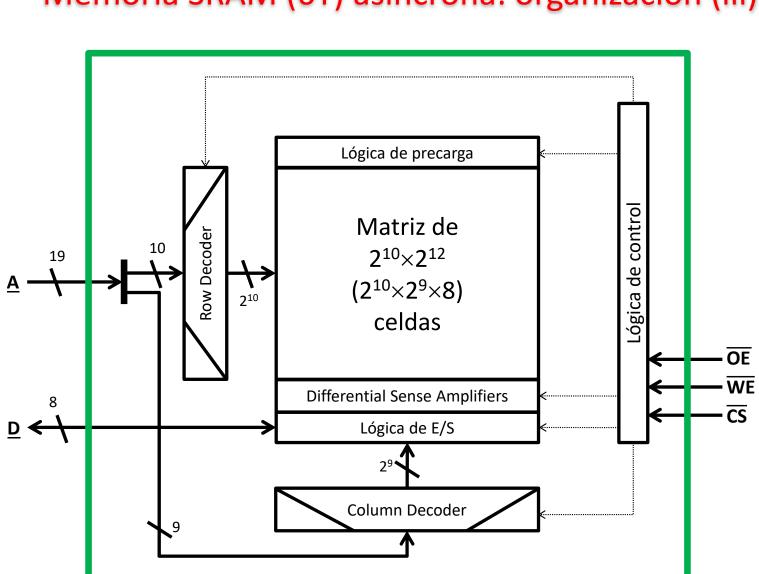

Memoria SRAM asíncrona (6T): organización (ii)

- Una misma organización física de celdas puede presentarse al exterior con diferentes organizaciones lógicas:

- Por ejemplo, toda SRAM de 16b se diseñaría con una matriz de 4x4 celdas.

## Aspectos tecnológicos

Memoria SRAM (6T) asíncrona: organización (iii)

**SRAM 4Mb (512K×8)**

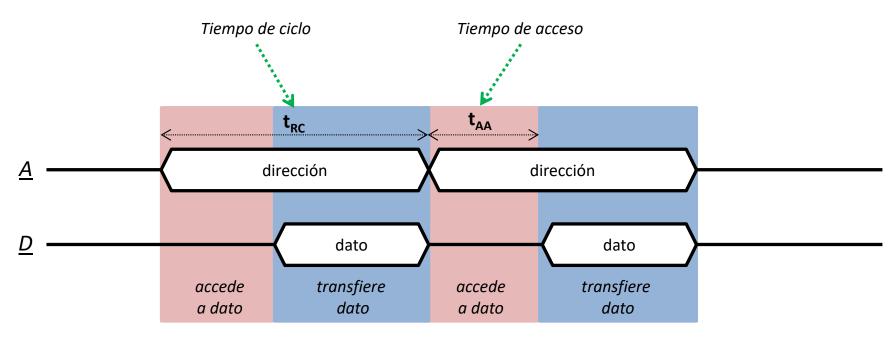

#### Ciclo de acceso SRAM asíncrona (1964)

- SRAM (asíncrona): para acceder un dato basta con indicar su dirección.

- Con las señales <del>OE</del> y <del>WE</del> (o R/<del>W</del>) se indica si el acceso es de lectura o de escritura.

Ciclo de acceso simplificado

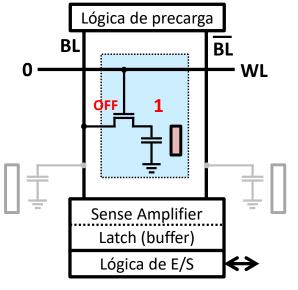

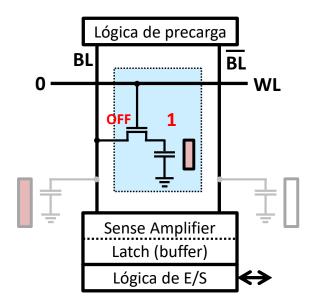

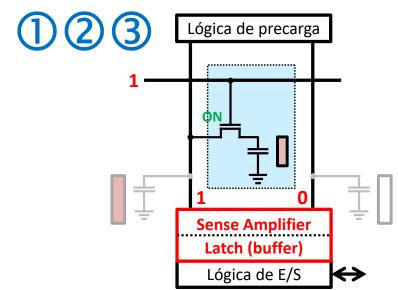

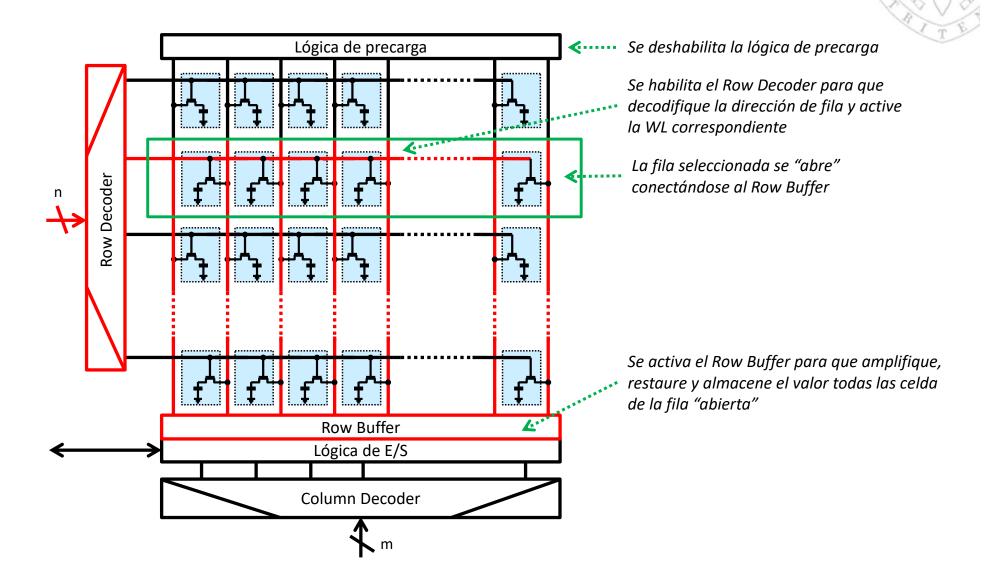

#### Celda DRAM 1T: lectura

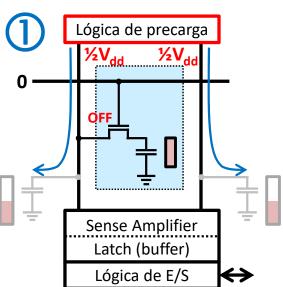

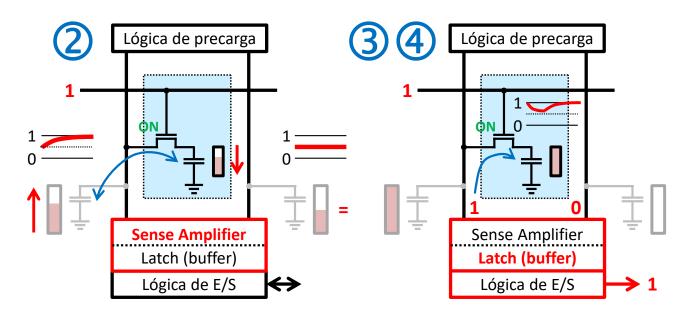

- 1. Precharge: Se precargan a ½Vdd ambas BL

- 2. Activate (Row Access): Se activan WL y sense amplifier:

- La celda comparte carga con BL destruyendo el valor almacenado.

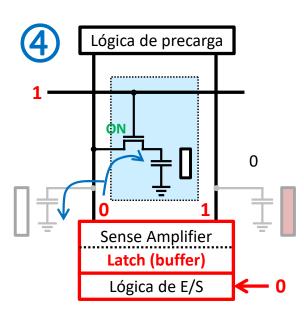

- 3. Se amplifica la pequeña diferencia de voltaje entre ambas BL.

- o Restaurando en la celda el valor leído.

- 4. Read (Column Access): Se transfiere al exterior el valor leído

- Este valor se conserva en el buffer del amplificador.

- Se desactivan WL y sense amplifier.

FC-2

## Aspectos tecnológicos

#### Celda DRAM 1T: escritura

- Comienza como una lectura (Precharge+Activate).

- Pero el valor leído no se transfiere al exterior.

- 4. Write (Column Access): El valor a almacenar se sobrescribe en el buffer del amplificador.

- El valor almacenado en el buffer se propaga por la BL:

- o La celda se carga/descarga en función del valor a almacenar.

- Se desactivan WL y sense amplifier.

## Aspectos tecnológicos

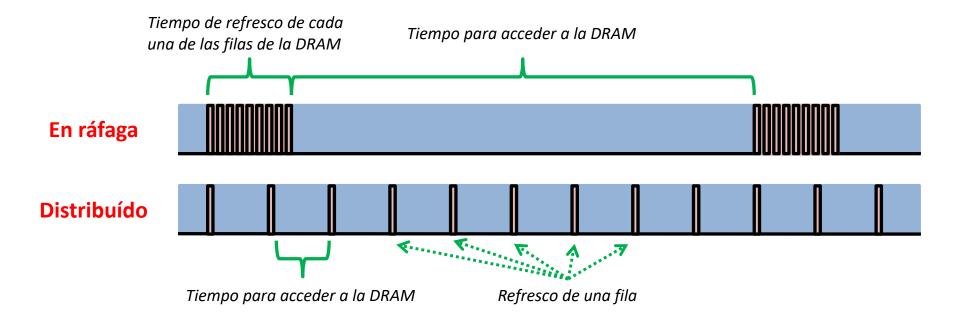

#### Celda DRAM 1T: refresco

- La celda si no se lee/escribe, pierde gradualmente su carga.

- Los 1 se convierten en 0 transcurrido cierto tiempo de inactividad.

- Para evitarlo, toda celda deber ser refrescada periódicamente (64 ms)

- Dado que toda lectura reestablece el valor de la celda, el refresco se hace mediante lecturas sin transferencia al exterior (Precharge+Activate)

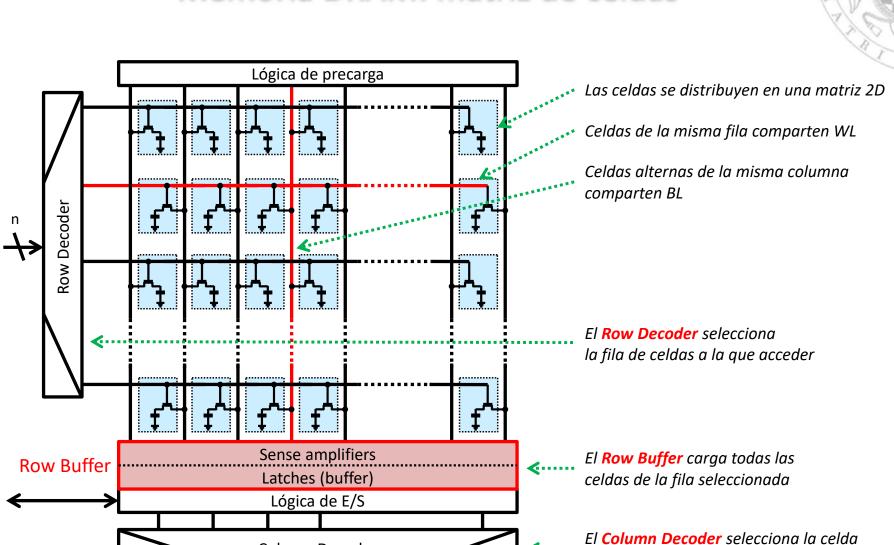

Memoria DRAM: matriz de celdas

del Row Buffer que se conecta al exterior

Column Decoder

FC-2

## **FC-2** *Sistemo*

## Aspectos tecnológicos

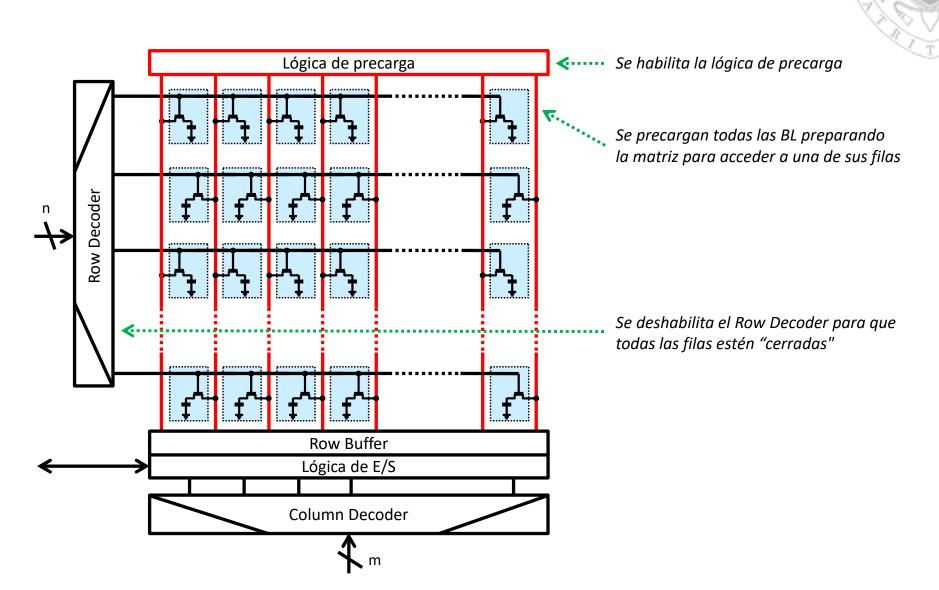

Memoria DRAM: Precharge

## Aspectos tecnológicos

Memoria DRAM: Activate (Row Access)

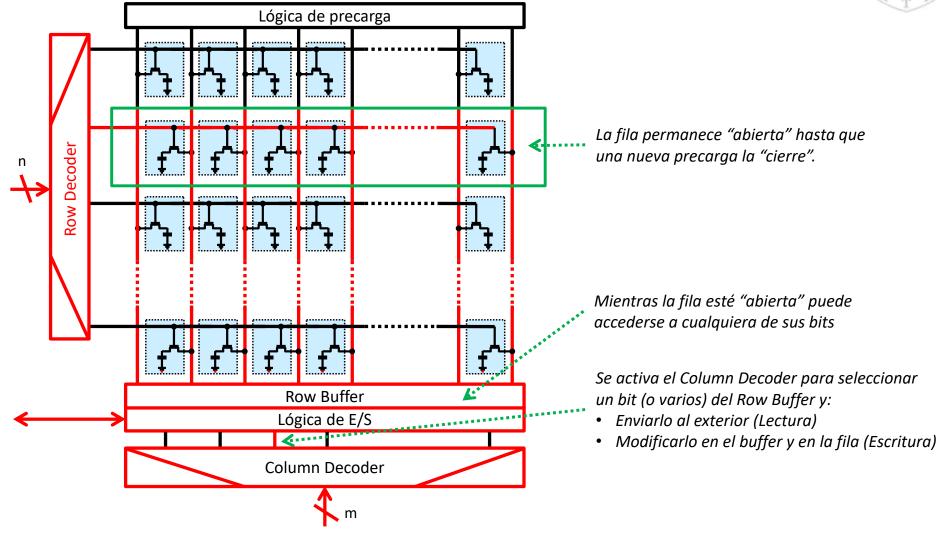

Memoria DRAM: Read / Write (Column Access)

FC-2

## Aspectos tecnológicos

Memoria DRAM: Refresh

- El refresco se realiza por filas mediante ciclos de Precarga+Activate que lanza la propia memoria (Seft-Refresh) o un controlador externo.

- El refresco de la memoria completa puede hacerse:

- En ráfaga: Todas las filas de la DRAM se refrescan consecutivamente.

- La memoria está inaccesible durante un largo periodos de tiempo.

- Distribuido: Se espacia el refresco de cada fila (o grupo de ellas).

- Los accesos deben intercalarse entre los ciclos de refresco.

## Aspectos tecnológicos

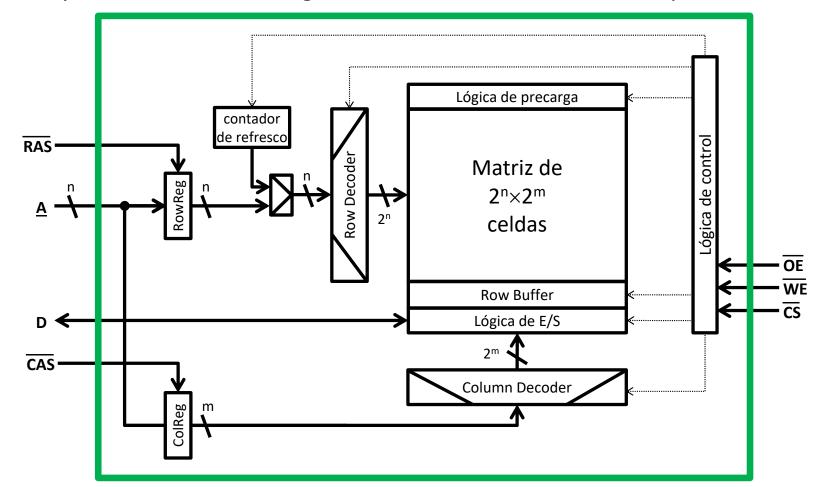

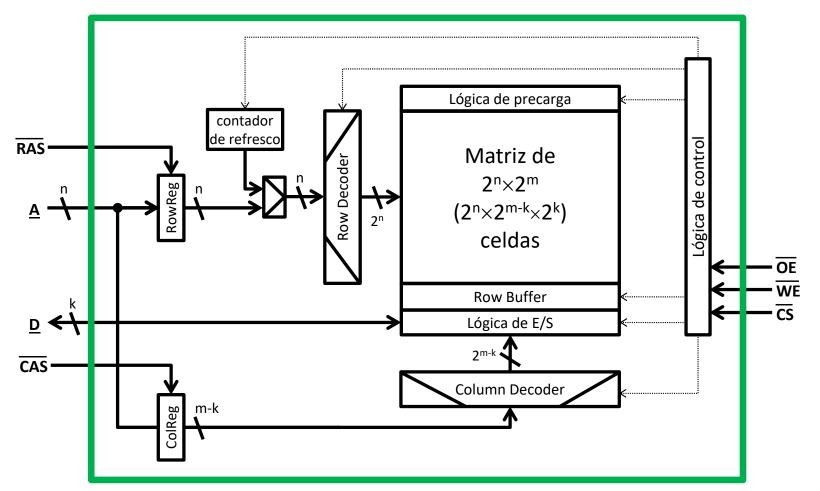

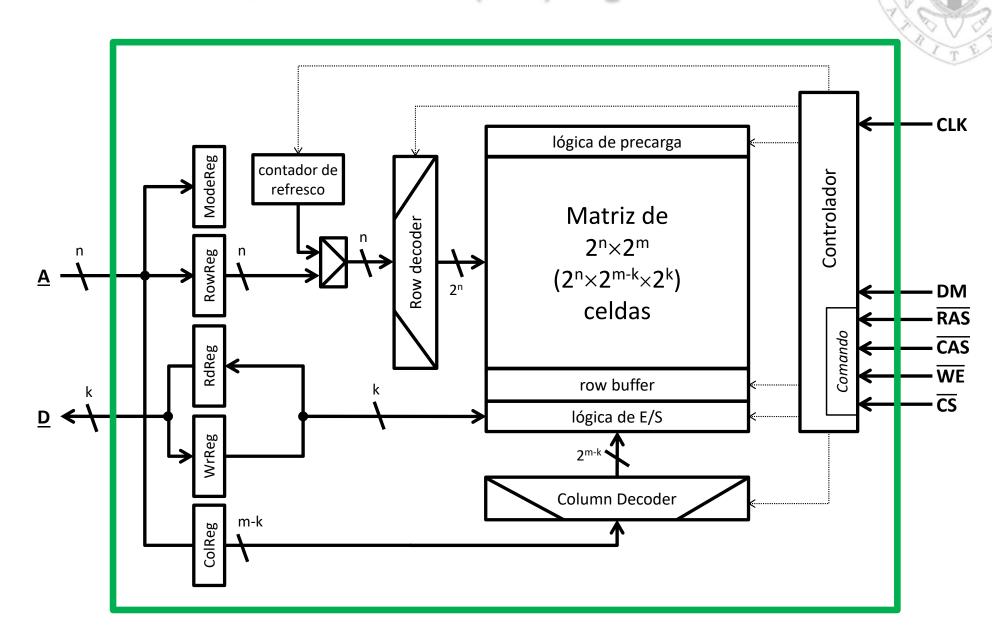

#### Memoria DRAM asíncrona: organización

- Las celdas se distribuyen en una matriz 2<sup>n</sup>×2<sup>m</sup> (con n≈m)

- o n (fila) y m (columna) se envían en instantes distintos por los mismos pines.

- o n y m se obtienen de fragmentar en 2 la dirección enviada por la CPU.

## Aspectos tecnológicos

#### Memoria DRAM asíncrona: organización

- En general, la organización física de las celdas de DRAM es independiente de la organización lógica de los datos.

- Las DRAM suelen tener interfaces estrechos de datos k = (1b, 4b, 8b ó 16b)

66

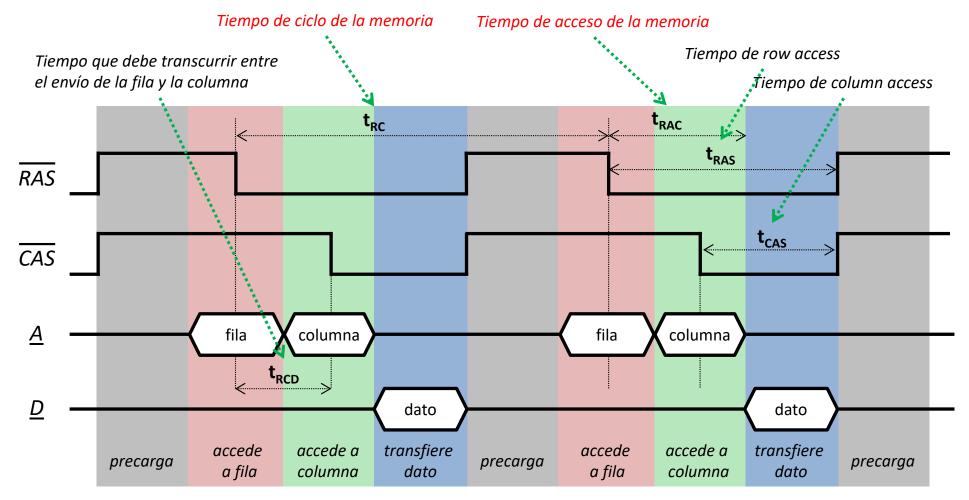

DRAM (asíncrona): el acceso a cualquier dato siempre requiere indicar tanto su fila como su columna.

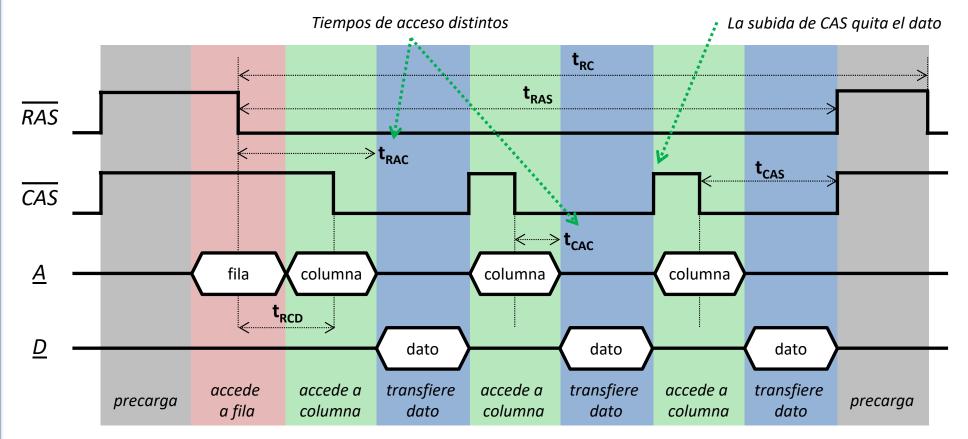

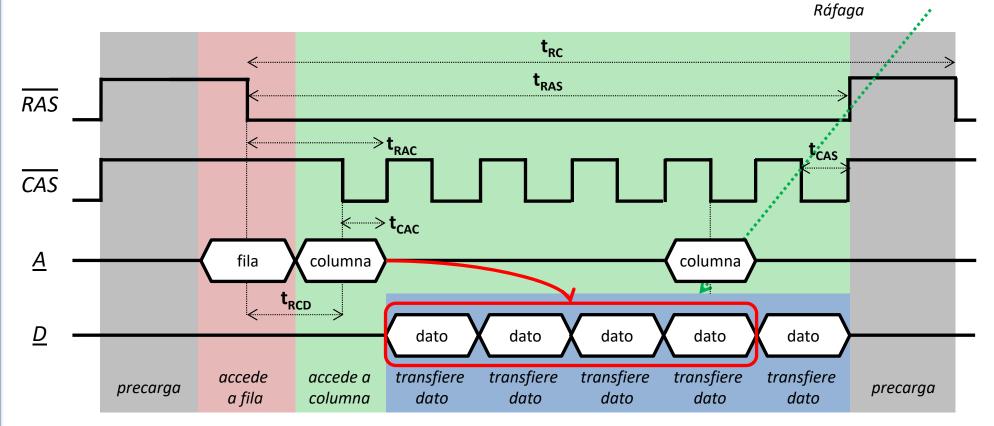

#### Ciclo de acceso FPM DRAM (1986)

- FPM (fast page mode) DRAM: el acceso a datos de una misma fila requiere indicar únicamente la columna.

- Solo en el primer acceso a la fila se indica fila y columna.

- o Este primer acceso es lento, los sucesivos más rápidos.

## ponus:

#### FC-2

68

## Aspectos tecnológicos

Ciclo de acceso EDO DRAM (1995)

- EDO (Extended Data Output) DRAM: permite indicar una nueva columna durante la transferencia de la anterior.

- Acelera el acceso a datos de la misma fila.

t<sub>RC</sub> t<sub>RAS</sub> RAS  $\Rightarrow$   $\mathbf{t}_{\mathsf{RAC}}$  $t_{CAS}$ CAS <−−> t<sub>CAC</sub> Α fila columna columna columna columna columna dato dato dato dato accede a transfiere transfiere transfiere transfiere accede precarga precarga a fila dato dato dato columna dato

El dato permanece tras la subida de CAS

Ciclo de acceso simplificado

Ciclo de acceso BEDO DRAM (1997)

- BEDO (Burst EDO) DRAM: una vez indicada la columna, se accede a las columnas siguientes en ráfaga (burst).

- Tiene un contador de columna interno que se actualiza en cada acceso.

- El envío de una nueva columna inicia la ráfaga y finaliza la anterior.

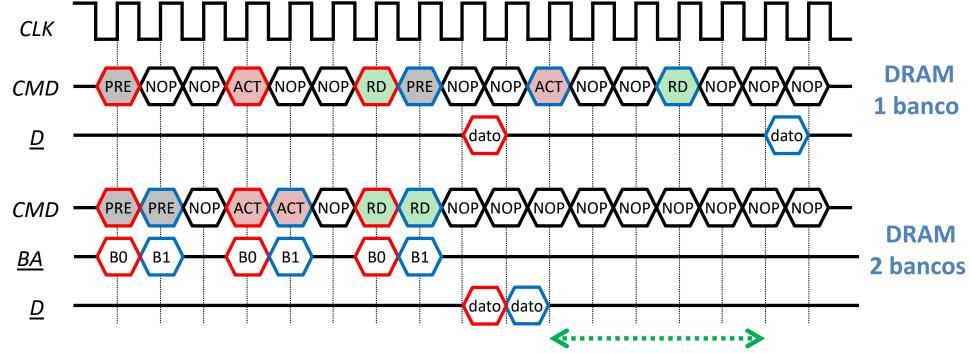

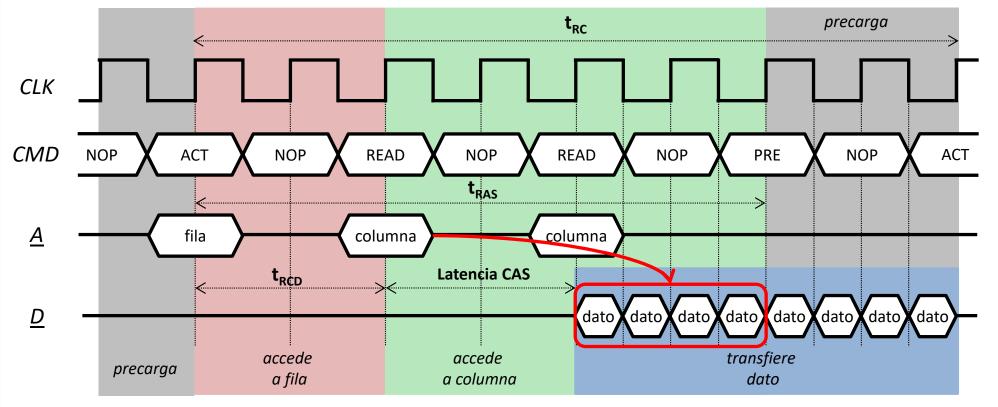

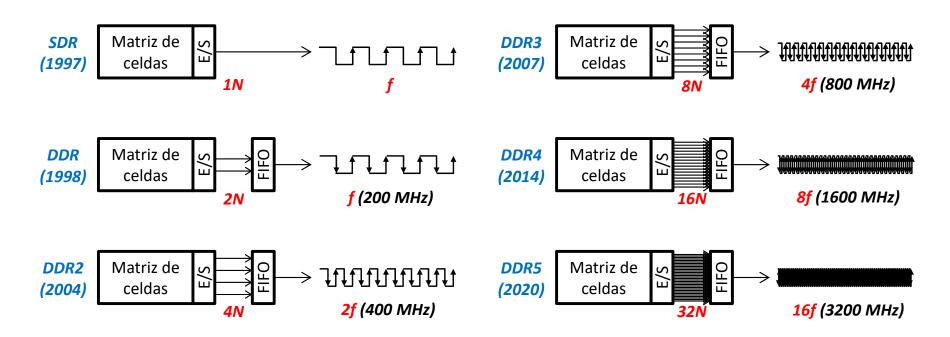

Ciclo de acceso SDRAM (SDR, 1997)

- SDRAM (Synchronous DRAM): memoria DRAM con interfaz síncrono.

- Desacopla el interfaz de la compleja generación de pulsos asíncronos.

- Se controla por comandos codificados en las líneas: CS, RAS, CAS, WE...

Los comandos y direcciones se cargan Los datos se transfieren síncronamente en en los flancos de subida de un reloj ráfagas transcurridos un cierto número de ciclos  $t_{RC}$ precarga CLK **CMD** ACT NOP NOP **READ** NOP NOP **ACT** READ NOP t<sub>RAS</sub> <u>A</u> fila columna columna Latencia CAS  $\tau_{RCD}$ <u>D</u> dato dato dato dato transfiere accede accede precarga a fila a columna dato

Ciclo de acceso simplificado

**EC-2** *Sistem*

## Aspectos tecnológicos

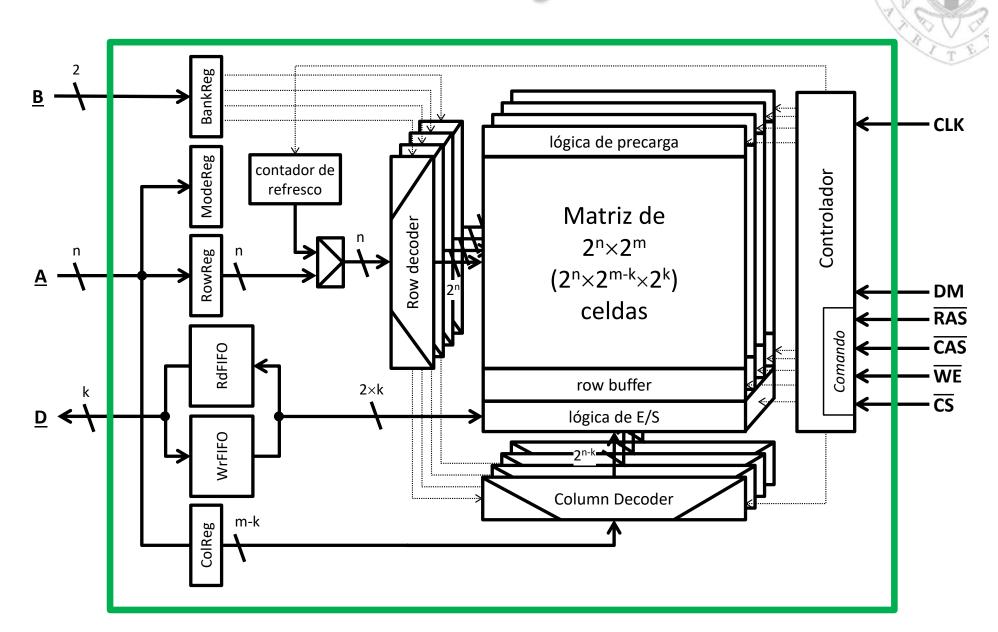

Memoria SDRAM (SDR): organización

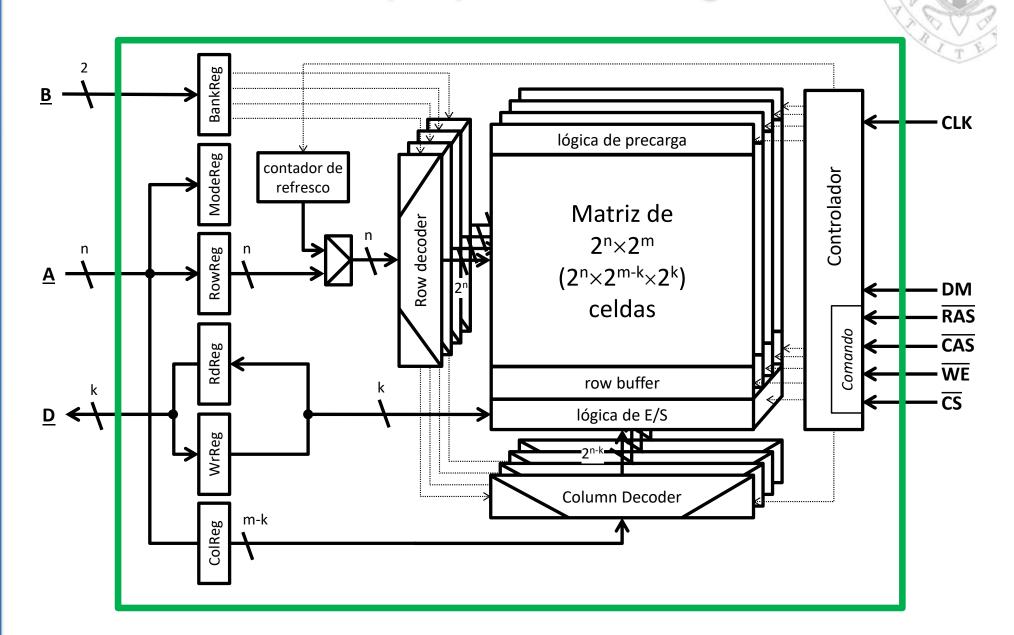

#### Memorias SDRAM (SDR) multibanco

- Para ocultar la latencia de acceso a los datos las SDRAM se organizan internamente en bancos accesibles en paralelo.

- O Un banco es una matriz de celdas distinta que opera independientemente.

- o Los bancos comparten pines de comando, dirección y de datos.

- Añade una línea para indicar el banco a quien van dirigidos los comandos.

Memoria SDRAM (SDR) de 4 bancos: organización

## Sistema de memoria ponus:

#### FC-2

74

### Aspectos tecnológicos

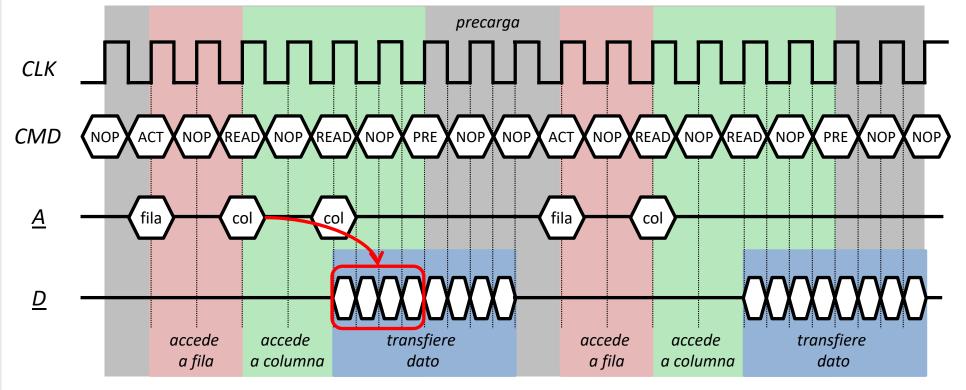

Ciclo de acceso DDR (DDR1, 1998)

- DDR (*Double Data Rate*): memoria SDRAM que aprovecha ambos flacos de reloj para transmitir datos.

- o Por cada acceso a columna, se captan (prefetch) 2 datos del Row Buffer.

- Duplica la tasa de transferencia sin aumentar la frecuencia de reloj.

## Aspectos tecnológicos

Memoria DDR: organización

76

## Aspectos tecnológicos

Ciclo de acceso DDR2 (2004)

- DDR2 (Double Data Rate 2): duplica la frecuencia del interfaz respecto a la DDR manteniendo la velocidad de acceso a la matriz de celdas.

- Por cada acceso a columna, se captan (prefetch) 4 datos del Row Buffer.

- El interfaz alcanza frecuencias de reloj de hasta 400 MHz.

#### Generaciones de memorias DDR

- En las sucesivas generaciones de DDR el tiempo de acceso a la matriz de celdas ha permanecido prácticamente constante.

- Sin embargo la tasa de transferencia ha crecido exponencialmente:

- O Cada generación duplica la frecuencia del interfaz.

- Duplicando la cantidad de datos captados del Row Buffer por cada acceso.

## Aspectos tecnológicos

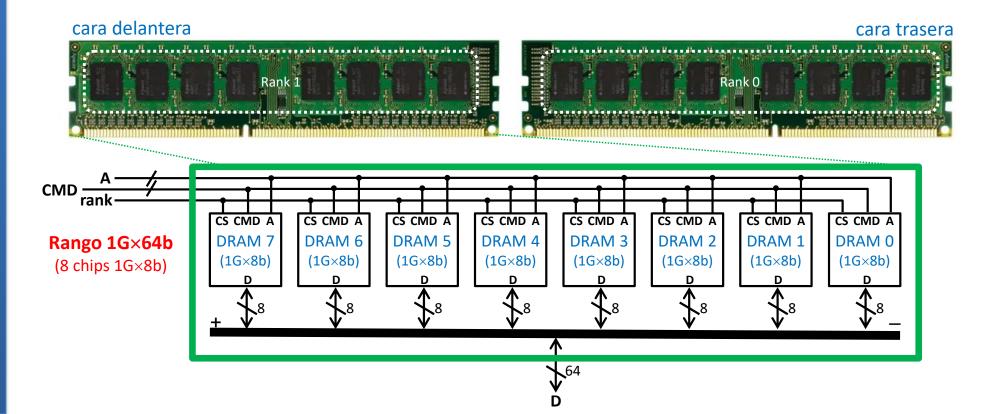

#### Módulos de memoria SDRAM

- Los interfaces de datos de los chips de SDRAM son estrechos (4/8/16b)

- O Se organizan en rangos (ranks) para formar un interfaces más anchos

- Se activan a la vez, comparten dirección y comando, los datos se unen en paralelo.

- Los rangos se agrupan en módulos DIMM (Dual Inline Memory Module)

- Comparten dirección, comando y datos pero se seleccionan independientemente.

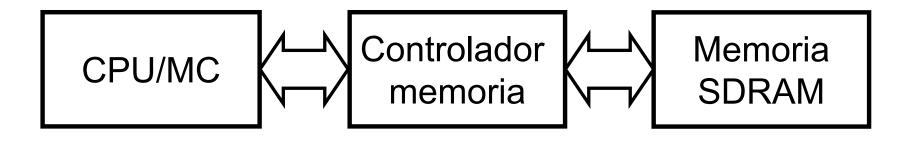

#### Controlador de memoria

- El interfaz de las memorias SDRAM es tan complejo que la CPU/MC se conecta a ella a través de un controlador de memoria que:

- o Recibe y sirve peticiones de acceso por parte de la CPU/MC.

- o Transforma estas peticiones en secuencias de comandos.

- Almacena los comandos y reordena su envío para mejorar el rendimiento.

- Llevando pista del estado de cada rango, banco, fila, etc...

- Intercalando accesos con los ciclos de refresco.

- Respetando las múltiples (+50) ligaduras físicas de tiempo existentes.

- Gestiona errores de lectura.

- Supervisa el consumo y temperatura de la SDRAM.

#### Memorias SRAM vs DRAM (DDRx)

| Característica           | SRAM                | DRAM (DDRx)         |

|--------------------------|---------------------|---------------------|

| Transistores/bit         | 6T/b (2 terminales) | 1T/b (1 terminal)   |

| Tiempo de acceso a celda | Muy bajo y fijo     | Alto y variable     |

| Densidad de integración  | Baja                | Muy alta            |

| Ubicación                | On-chip             | Off-chip            |

| Coste/bit                | Alto                | Вајо                |

| Lectura                  | No destructiva      | Destructiva         |

| Necesidad de refresco    | No                  | Si                  |

| Organización de celdas   | 2D                  | 3D (multibanco)     |

| Dirección multiplexada   | No                  | Si                  |

| Interfaz                 | Simple y asíncrono  | Complejo y síncrono |

### Acerca de Creative Commons

- Ofrece algunos derechos a terceras personas bajo ciertas condiciones. Este documento tiene establecidas las siguientes:

- Reconocimiento (Attribution):

En cualquier explotación de la obra autorizada por la licencia hará falta reconocer la autoría.

- No comercial (Non commercial):

La explotación de la obra queda limitada a usos no comerciales.

- Compartir igual (Share alike): La explotación autorizada incluye la creación de obras derivadas siempre que mantengan la misma licencia al ser divulgadas.

Más información: https://creativecommons.org/licenses/by-nc-sa/4.0/

FC-2