## **Problemas Tema 4:**

# Diseño del formato de instrucción

### Fernando Castro Rodríguez

Dpto. Arquitectura de Computadores y Automática Universidad Complutense de Madrid

- 1) Cada una de las siguientes instrucciones del repertorio de ensamblador de RISC-V, ¿con qué secuencia de 32 bits se corresponde en código máquina?

- a) lw t0, 0(t2)

- b) bge t1,t0,0x2C

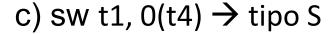

- c) sw t1,0(t4)

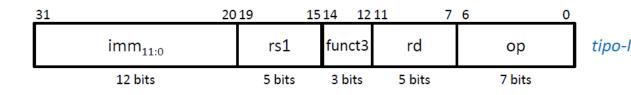

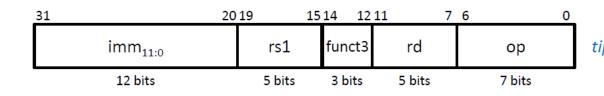

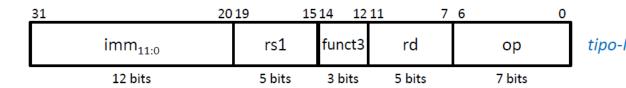

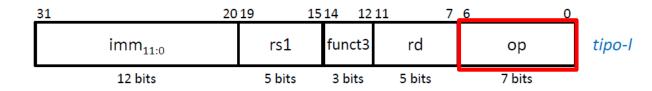

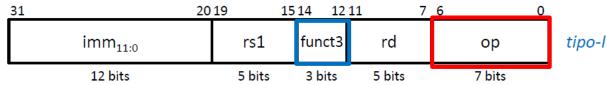

a) lw t0,  $0(t2) \rightarrow tipo l$

| 31 20               | 19     | 15 14 12 | 11 7   | 6 0    | _      |

|---------------------|--------|----------|--------|--------|--------|

| imm <sub>11:0</sub> | rs1    | funct3   | rd     | ор     | tipo-l |

| 12 bits             | 5 bits | 3 bits   | 5 bits | 7 bits | -      |

# Codificación de campos

Códigos de función (i)

|           | 100    |         | -01  | 200    |

|-----------|--------|---------|------|--------|

| Instrucci | ones c | e carga | de m | emoria |

| ор      | funct3 | Instrucción | Tipo |

|---------|--------|-------------|------|

|         | 000    | lb          | 1    |

|         | 001    | lh          | 1    |

| 0000011 | 010    | lw          | 1    |

|         | 011    | lbu         | I    |

|         | 100    | lhu         | 1    |

| 010 | 0000011 |

|-----|---------|

## a) lw t0, $0(t2) \rightarrow tipo l$

p-1

| 010 00101 | 0000011 |

|-----------|---------|

|-----------|---------|

# Codificación de campos

| Nombre | Número | Código |

|--------|--------|--------|

| zero   | x0     | 00000  |

| ra     | x1     | 00001  |

| sp     | x2     | 00010  |

| gp     | х3     | 00011  |

| tp     | x4     | 00100  |

| t0     | x5     | 00101  |

| t1     | х6     | 00110  |

| t2     | x7     | 00111  |

| s0/fp  | x8     | 01000  |

| s1     | x9     | 01001  |

| a0     | x10    | 01010  |

| a1     | x11    | 01011  |

| a2     | x12    | 01100  |

| a3     | x13    | 01101  |

| a4     | x14    | 01110  |

| a5     | x15    | 01111  |

| Nombre | Número | Código |

|--------|--------|--------|

| a6     | x16    | 10000  |

| a7     | x17    | 10001  |

| s2     | x18    | 10010  |

| s3     | x19    | 10011  |

| s4     | x20    | 10100  |

| s5     | x21    | 10101  |

| s6     | x22    | 10110  |

| s7     | x23    | 10111  |

| s8     | x24    | 11000  |

| s9     | x25    | 11001  |

| s10    | x26    | 11010  |

| s11    | x27    | 11011  |

| t3     | x28    | 11100  |

| t4     | x29    | 11101  |

| t5     | x30    | 11110  |

| t6     | x31    | 11111  |

# a) lw t0, $0(t2) \rightarrow tipo I$

tipo-l

00111

010 00101

0000011

## Codificación de campos

| Nombre     | Número | Código |

|------------|--------|--------|

| zero       | х0     | 00000  |

| ra         | x1     | 00001  |

| sp         | x2     | 00010  |

| gp         | х3     | 00011  |

| tp         | x4     | 00100  |

| t0         | x5     | 00101  |

| t1         | х6     | 00110  |

| t2         | x7     | 00111  |

| s0/fp      | х8     | 01000  |

| <b>s</b> 1 | x9     | 01001  |

| a0         | x10    | 01010  |

| a1         | x11    | 01011  |

| a2         | x12    | 01100  |

| a3         | x13    | 01101  |

| a4         | x14    | 01110  |

| a5         | x15    | 01111  |

| Nombre | Número | Código |

|--------|--------|--------|

| a6     | x16    | 10000  |

| a7     | x17    | 10001  |

| s2     | x18    | 10010  |

| s3     | x19    | 10011  |

| s4     | x20    | 10100  |

| s5     | x21    | 10101  |

| s6     | x22    | 10110  |

| s7     | x23    | 10111  |

| s8     | x24    | 11000  |

| s9     | x25    | 11001  |

| s10    | x26    | 11010  |

| s11    | x27    | 11011  |

| t3     | x28    | 11100  |

| t4     | x29    | 11101  |

| t5     | x30    | 11110  |

| t6     | x31    | 11111  |

a) lw t0,  $O(t2) \rightarrow tipo I$

00000000000 00111 010 00101 0000011

0x0003A283

- 1) Cada una de las siguientes instrucciones del repertorio de ensamblador de RISC-V, ¿con qué secuencia de 32 bits se corresponde en código máquina?

- a) lw t0, 0(t2)

- b) bge t1,t0,0x2C

- c) Sw t1,0(t4)

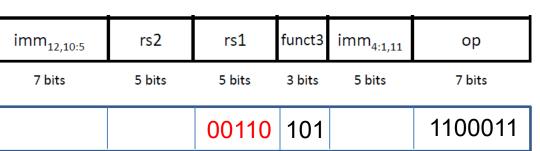

| imm <sub>12,10:5</sub> | rs2    | rs1    | funct3 | imm <sub>4:1,11</sub> | ор      | tipo-B |

|------------------------|--------|--------|--------|-----------------------|---------|--------|

| 7 bits                 | 5 bits | 5 bits | 3 bits | 5 bits                | 7 bits  |        |

|                        |        |        | 101    |                       | 1100011 |        |

#### Instrucciones de salto condicional

| ор      | funct3 | Instrucción | Tipo |

|---------|--------|-------------|------|

| 1100011 | 000    | peq         | В    |

|         | 001    | bne         | В    |

|         | 100    | blt         | В    |

|         | 101    | bge         | В    |

|         | 110    | bltu        | В    |

|         | 111    | bgeu        | В    |

FC-2

b) bge t1,t0, $0x2C \rightarrow tipo B$

| imm <sub>12,10:5</sub> | rs2    | rs1    | funct3 | imm <sub>4:1,11</sub> | ор      |

|------------------------|--------|--------|--------|-----------------------|---------|

| 7 bits                 | 5 bits | 5 bits | 3 bits | 5 bits                | 7 bits  |

|                        |        | 00110  | 101    |                       | 1100011 |

tipo-B

# Codificación de campos

| Nombre | Número | Código |

|--------|--------|--------|

| zero   | х0     | 00000  |

| ra     | x1     | 00001  |

| sp     | x2     | 00010  |

| gp     | х3     | 00011  |

| tp     | x4     | 00100  |

| t0     | x5     | 00101  |

| t1     | х6     | 00110  |

| t2     | х7     | 00111  |

| s0/fp  | x8     | 01000  |

| s1     | x9     | 01001  |

| a0     | x10    | 01010  |

| a1     | x11    | 01011  |

| a2     | x12    | 01100  |

| a3     | x13    | 01101  |

| a4     | x14    | 01110  |

| a5     | x15    | 01111  |

| Nombre | Número | Código |

|--------|--------|--------|

| a6     | x16    | 10000  |

| a7     | x17    | 10001  |

| s2     | x18    | 10010  |

| s3     | x19    | 10011  |

| s4     | x20    | 10100  |

| s5     | x21    | 10101  |

| s6     | x22    | 10110  |

| s7     | x23    | 10111  |

| s8     | x24    | 11000  |

| s9     | x25    | 11001  |

| s10    | x26    | 11010  |

| s11    | x27    | 11011  |

| t3     | x28    | 11100  |

| t4     | x29    | 11101  |

| t5     | x30    | 11110  |

| t6     | x31    | 11111  |

| imm <sub>12,10:5</sub> | rs2    | rs1    | funct3 | imm <sub>4:1,11</sub> | ор      |

|------------------------|--------|--------|--------|-----------------------|---------|

| 7 bits                 | 5 bits | 5 bits | 3 bits | 5 bits                | 7 bits  |

|                        | 00101  | 00110  | 101    |                       | 1100011 |

tipo-B

| Nombre | Número | Código |

|--------|--------|--------|

| zero   | х0     | 00000  |

| ra     | x1     | 00001  |

| sp     | x2     | 00010  |

| gp     | х3     | 00011  |

| tp     | x4     | 00100  |

| t0     | x5     | 00101  |

| t1     | х6     | 00110  |

| t2     | x7     | 00111  |

| s0/fp  | x8     | 01000  |

| s1     | x9     | 01001  |

| a0     | x10    | 01010  |

| a1     | x11    | 01011  |

| a2     | x12    | 01100  |

| a3     | x13    | 01101  |

| a4     | x14    | 01110  |

| a5     | x15    | 01111  |

| Nombre | Número | Código |

|--------|--------|--------|

| a6     | x16    | 10000  |

| a7     | x17    | 10001  |

| s2     | x18    | 10010  |

| s3     | x19    | 10011  |

| s4     | x20    | 10100  |

| s5     | x21    | 10101  |

| s6     | x22    | 10110  |

| s7     | x23    | 10111  |

| s8     | x24    | 11000  |

| s9     | x25    | 11001  |

| s10    | x26    | 11010  |

| s11    | x27    | 11011  |

| t3     | x28    | 11100  |

| t4     | x29    | 11101  |

| t5     | x30    | 11110  |

| t6     | x31    | 11111  |

| imm <sub>12,10:5</sub> | rs2    | rs1    | funct3 | imm <sub>4:1,11</sub> | ор      |

|------------------------|--------|--------|--------|-----------------------|---------|

| 7 bits                 | 5 bits | 5 bits | 3 bits | 5 bits                | 7 bits  |

|                        | 00101  | 00110  | 101    |                       | 1100011 |

0x2C → 0b000000101100

| imm <sub>12,10:5</sub> | rs2    | rs1    | funct3 | imm <sub>4:1,11</sub> | ор      |

|------------------------|--------|--------|--------|-----------------------|---------|

| 7 bits                 | 5 bits | 5 bits | 3 bits | 5 bits                | 7 bits  |

|                        | 00101  | 00110  | 101    | 01100                 | 1100011 |

$0x2C \rightarrow 0b000000101100$

${\rm imm}_{12,10:5}$ imm<sub>4:1,11</sub> rs2 rs1 funct3 op 7 bits 7 bits 5 bits 5 bits 3 bits 5 bits 1100011 01100 00101 00110 101 0000001

tipo-B

0x2C → 0b000000101100

- 1) Cada una de las siguientes instrucciones del repertorio de ensamblador de RISC-V, ¿con qué secuencia de 32 bits se corresponde en código máquina?

- lw t0, 0(t2)

- bge t1,t0,0x2C

- sw t1,0(t4)

| imm <sub>11:5</sub> | rs2 | rs1 | funct3 | imm <sub>4:0</sub> | ор | tipo-S |

|---------------------|-----|-----|--------|--------------------|----|--------|

| 010 010001 |

|------------|

|------------|

### Instrucciones de almacenaje en memoria

| ор      | funct3 | Instrucción | Tipo |

|---------|--------|-------------|------|

|         | 000    | sb          | S    |

| 0100011 | 001    | sh          | S    |

|         | 010    | sw          | S    |

### c) sw t1, $0(t4) \rightarrow tipo S$

| imm <sub>11:5</sub> | rs2 | rs1   | funct3 | imm <sub>4:0</sub> | ор      |

|---------------------|-----|-------|--------|--------------------|---------|

|                     |     |       |        |                    |         |

|                     |     | 11101 | 010    |                    | 0100011 |

# tipo-S

# Codificación de campos

| Nombre | Número | Código |

|--------|--------|--------|

| zero   | х0     | 00000  |

| ra     | x1     | 00001  |

| sp     | x2     | 00010  |

| gp     | х3     | 00011  |

| tp     | x4     | 00100  |

| t0     | x5     | 00101  |

| t1     | х6     | 00110  |

| t2     | x7     | 00111  |

| s0/fp  | x8     | 01000  |

| s1     | x9     | 01001  |

| a0     | x10    | 01010  |

| a1     | x11    | 01011  |

| a2     | x12    | 01100  |

| a3     | x13    | 01101  |

| a4     | x14    | 01110  |

| a5     | x15    | 01111  |

| Nombre | Número | Código |

|--------|--------|--------|

| a6     | x16    | 10000  |

| a7     | x17    | 10001  |

| s2     | x18    | 10010  |

| s3     | x19    | 10011  |

| s4     | x20    | 10100  |

| s5     | x21    | 10101  |

| s6     | x22    | 10110  |

| s7     | x23    | 10111  |

| s8     | x24    | 11000  |

| s9     | x25    | 11001  |

| s10    | x26    | 11010  |

| s11    | x27    | 11011  |

| t3     | x28    | 11100  |

| t4     | x29    | 11101  |

| t5     | x30    | 11110  |

| t6     | x31    | 11111  |

### c) sw t1, $0(t4) \rightarrow tipo S$

| imm <sub>11:5</sub> | rs2 | rs1 | funct3 | imm <sub>4:0</sub> | ор |

|---------------------|-----|-----|--------|--------------------|----|

|                     |     |     |        |                    | -  |

11101

00110

010

# tipo-S

0100011

# Codificación de campos

| Nombre | Número | Código |

|--------|--------|--------|

| zero   | х0     | 00000  |

| ra     | x1     | 00001  |

| sp     | x2     | 00010  |

| gp     | х3     | 00011  |

| tp     | x4     | 00100  |

| t0     | x5     | 00101  |

| t1     | х6     | 00110  |

| t2     | x7     | 00111  |

| s0/fp  | x8     | 01000  |

| s1     | x9     | 01001  |

| a0     | x10    | 01010  |

| a1     | x11    | 01011  |

| a2     | x12    | 01100  |

| a3     | x13    | 01101  |

| a4     | x14    | 01110  |

| a5     | x15    | 01111  |

| Nombre | Número | Código |

|--------|--------|--------|

| a6     | x16    | 10000  |

| a7     | x17    | 10001  |

| s2     | x18    | 10010  |

| s3     | x19    | 10011  |

| s4     | x20    | 10100  |

| s5     | x21    | 10101  |

| s6     | x22    | 10110  |

| s7     | x23    | 10111  |

| s8     | x24    | 11000  |

| s9     | x25    | 11001  |

| s10    | x26    | 11010  |

| s11    | x27    | 11011  |

| t3     | x28    | 11100  |

| t4     | x29    | 11101  |

| t5     | x30    | 11110  |

| t6     | x31    | 11111  |

c) sw t1,  $O(t4) \rightarrow tipo S$

| imm <sub>11:5</sub> | rs2   | rs1   | funct3 | imm <sub>4:0</sub> | ор      |   |

|---------------------|-------|-------|--------|--------------------|---------|---|

|                     |       |       |        |                    |         | • |

| 0000000             | 00110 | 11101 | 010    | 00000              | 0100011 |   |

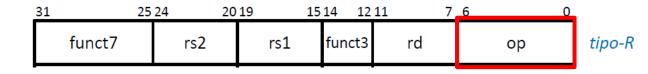

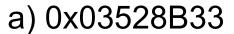

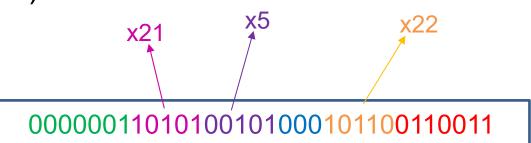

- 2) Cada una de las siguientes secuencias de 32 bits, ¿con qué instrucciones del repertorio de ensamblador de RISC-V se corresponden?

- a) 0x03528B33

- b) 0x00190913

- c) 0x000006F

a) 0x03528B33

0000001101010010100010110011

- 2) Cada una de las siguientes secuencias de 32 bits, ¿con qué instrucciones del repertorio de ensamblador de RISC-V se corresponden?

- a) 0x03528B33

- b) 0x00190913

- c) 0x0000006F

a) 0x03528B33

0000001101010010100010110011

| ор      | Clase de instrucción                                              | Tipo |

|---------|-------------------------------------------------------------------|------|

| 0000011 | carga de memoria                                                  | 1    |

| 0010011 | aritmético-lógicas y de desplazamiento con operando inmediato     | 1    |

| 0010111 | auipc                                                             | U    |

| 0100011 | almacenaje en memoria                                             | S    |

| 0110011 | aritmético-lógicas y de desplazamiento con operandos en registros | R    |

| 0110111 | lui                                                               | U    |

| 1100011 | salto condicional                                                 | В    |

| 1100111 | jalr                                                              | I    |

| 1101111 | jal                                                               | J    |

FC-2

### FC-2

a) 0x03528B33

00000011010100101000101100110011

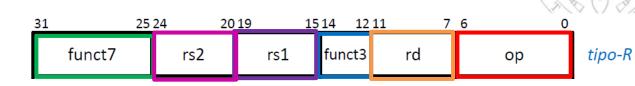

| 31     | 25 24 | 1 20 | 19 1 | 514 12 | 11 7 | 6 0 | _      |

|--------|-------|------|------|--------|------|-----|--------|

| funct7 |       | rs2  | rs1  | funct3 | rd   | ор  | tipo-R |

# Codificación de campos

Códigos de función (iv)

#### Instrucciones\* de multiplicación y división

| ор      | funct3 | funct7  | Instrucción | Tipo |

|---------|--------|---------|-------------|------|

|         | 000    | 0000001 | mul         | R    |

|         | 001    | 0000001 | mulh        | R    |

|         | 010    | 0000001 | mulhsu      | R    |

| 0110011 | 011    | 0000001 | mulhu       | R    |

| 0110011 | 100    | 0000001 | div         | R    |

|         | 101    | 0000001 | divu        | R    |

|         | 110    | 0000001 | rem         | R    |

|         | 111    | 0000001 | remu        | R    |

Instrucción mul

<sup>\*</sup>Definidas en la extension RVM

### Codificación de campos

Códigos de registro

| Nombre | Número     | Código |

|--------|------------|--------|

| zero   | х0         | 00000  |

| ra     | x1         | 00001  |

| sp     | x2         | 00010  |

| gp     | х3         | 00011  |

| tp     | x4         | 00100  |

| t0     | x5         | 00101  |

| t1     | х6         | 00110  |

| t2     | x7         | 00111  |

| s0/fp  | x8         | 01000  |

| s1     | <b>x</b> 9 | 01001  |

| a0     | x10        | 01010  |

| a1     | x11        | 01011  |

| a2     | x12        | 01100  |

| a3     | x13        | 01101  |

| a4     | x14        | 01110  |

| a5     | x15        | 01111  |

| Nombre | Número | Código |

|--------|--------|--------|

| a6     | x16    | 10000  |

| a7     | x17    | 10001  |

| s2     | x18    | 10010  |

| s3     | x19    | 10011  |

| s4     | x20    | 10100  |

| s5     | x21    | 10101  |

| s6     | x22    | 10110  |

| s7     | x23    | 10111  |

| s8     | x24    | 11000  |

| s9     | x25    | 11001  |

| s10    | x26    | 11010  |

| s11    | x27    | 11011  |

| t3     | x28    | 11100  |

| t4     | x29    | 11101  |

| t5     | x30    | 11110  |

| t6     | x31    | 11111  |

mul s6,t0,s5

FC-2

- 2) Cada una de las siguientes secuencias de 32 bits, ¿con qué instrucciones del repertorio de ensamblador de RISC-V se corresponden?

- a) 0x03528B33

- b) 0x00190913

- c) 0x000006F

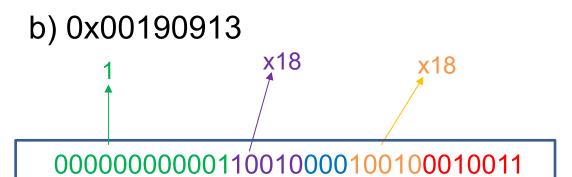

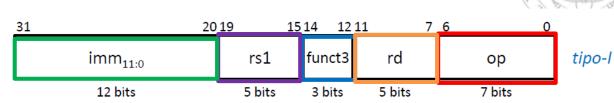

b) 0x00190913

00000000011001000010010011

- 2) Cada una de las siguientes secuencias de 32 bits, ¿con qué instrucciones del repertorio de ensamblador de RISC-V se corresponden?

- a) 0x03528B33

- b) 0x00190913

- c) 0x000006F

b) 0x00190913

000000000110010000100100011

| ор      | Clase de instrucción                                              | Tipo |

|---------|-------------------------------------------------------------------|------|

| 0000011 | carga de memoria                                                  | 1    |

| 0010011 | aritmético-lógicas y de desplazamiento con operando inmediato     | l    |

| 0010111 | auipc                                                             | U    |

| 0100011 | almacenaje en memoria                                             | S    |

| 0110011 | aritmético-lógicas y de desplazamiento con operandos en registros | R    |

| 0110111 | lui                                                               | U    |

| 1100011 | salto condicional                                                 | В    |

| 1100111 | jalr                                                              | I    |

| 1101111 | jal                                                               | J    |

FC-2

### b) 0x00190913

00000000011001000010010011

Instrucciones aritmético-lógicas y de desplazamiento con operando inmediato

| ор      | funct3 | funct7*  | Instrucción | Tipo |

|---------|--------|----------|-------------|------|

| 0010011 | 000    | -        | addi        | 1    |

|         | 001    | 0000000* | slli        | 1    |

|         | 010    | -        | slti        | 1    |

|         | 011    | -        | sltiu       | 1    |

|         | 100    | -        | xori        | 1    |

|         | 101    | 0000000* | srli        | 1    |

|         | 101    | 0100000* | srai        | 1    |

|         | 110    | -        | ori         | 1    |

|         | 111    | -        | andi        | I    |

FC-2

<sup>\*</sup>Codificados en los 7 bits superiores del campo imm

### Codificación de campos

Códigos de registro

| Nombre | Número     | Código |

|--------|------------|--------|

| zero   | х0         | 00000  |

| ra     | <b>x1</b>  | 00001  |

| sp     | x2         | 00010  |

| gp     | х3         | 00011  |

| tp     | x4         | 00100  |

| t0     | x5         | 00101  |

| t1     | х6         | 00110  |

| t2     | x7         | 00111  |

| s0/fp  | x8         | 01000  |

| s1     | <b>x</b> 9 | 01001  |

| a0     | x10        | 01010  |

| a1     | x11        | 01011  |

| a2     | x12        | 01100  |

| a3     | x13        | 01101  |

| a4     | x14        | 01110  |

| a5     | x15        | 01111  |

| Nombre | Número | Código |

|--------|--------|--------|

| a6     | x16    | 10000  |

| a7     | x17    | 10001  |

| s2     | x18    | 10010  |

| S3     | X19    | 10011  |

| s4     | x20    | 10100  |

| s5     | x21    | 10101  |

| s6     | x22    | 10110  |

| s7     | x23    | 10111  |

| s8     | x24    | 11000  |

| s9     | x25    | 11001  |

| s10    | x26    | 11010  |

| s11    | x27    | 11011  |

| t3     | x28    | 11100  |

| t4     | x29    | 11101  |

| t5     | x30    | 11110  |

| t6     | x31    | 11111  |

addi s2,s2,1

2) Cada una de las siguientes secuencias de 32 bits, ¿con qué instrucciones del repertorio de ensamblador de RISC-V se corresponden?

- a) 0x03528B33

- b) 0x00190913

- c) 0x0000006F

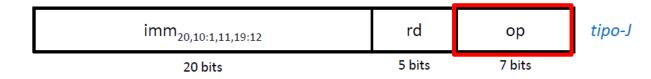

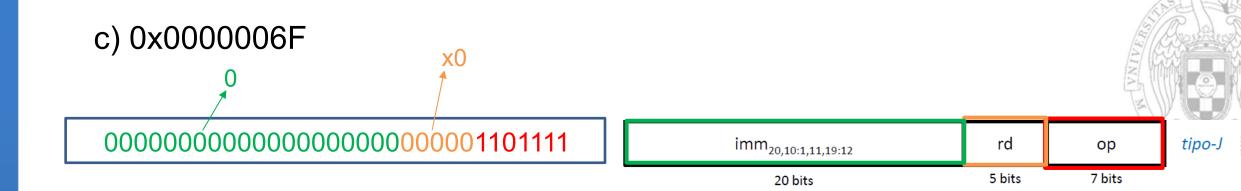

c) 0x0000006F

000000000000000000000001101111

- 2) Cada una de las siguientes secuencias de 32 bits, ¿con qué instrucciones del repertorio de ensamblador de RISC-V se corresponden?

- a) 0x03528B33

- b) 0x00190913

- c) 0x0000006F

c) 0x0000006F

000000000000000000000001101111

| ор      | Clase de instrucción                                              | Tipo |

|---------|-------------------------------------------------------------------|------|

| 0000011 | carga de memoria                                                  | - 1  |

| 0010011 | aritmético-lógicas y de desplazamiento con operando inmediato     | 1    |

| 0010111 | auipc                                                             | U    |

| 0100011 | almacenaje en memoria                                             | S    |

| 0110011 | aritmético-lógicas y de desplazamiento con operandos en registros | R    |

| 0110111 | lui                                                               | U    |

| 1100011 | salto condicional                                                 | В    |

| 1100111 | jalr                                                              |      |

| 1101111 | jal                                                               | J    |

# Acerca de *Creative Commons*

- Licencia CC (Creative Commons)

- Ofrece algunos derechos a terceras personas bajo ciertas condiciones. Este documento tiene establecidas las siguientes:

- Reconocimiento (Attribution):

En cualquier explotación de la obra autorizada por la licencia hará falta reconocer la autoría.

- No comercial (Non commercial):

La explotación de la obra queda limitada a usos no comerciales.

- Compartir igual (Share alike):

La explotación autorizada incluye la creación de obras derivadas siempre que mantengan la misma licencia al ser divulgadas.

Más información: https://creativecommons.org/licenses/by-nc-sa/4.0/