## diseño del interconexionado (iii)

Primera fase: Selección de interconexiones (cont.)

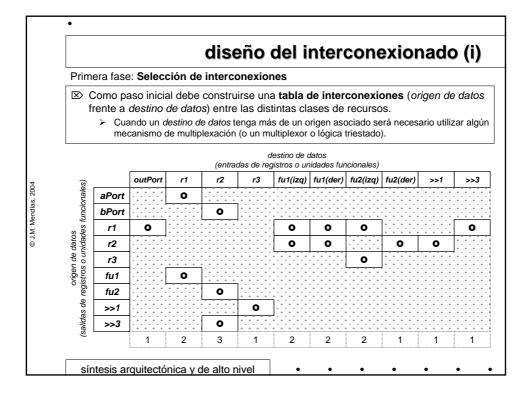

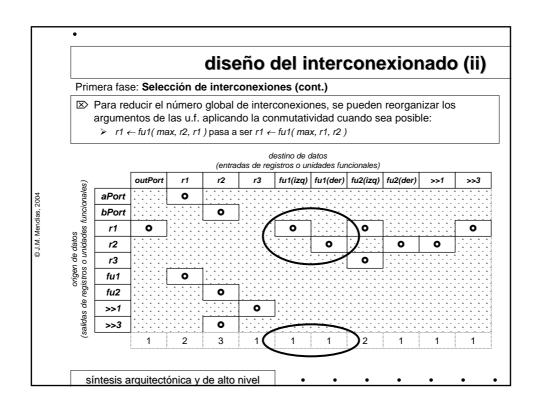

- ☑ En un sistema podemos encontrar 4 tipos de interconexiones 1:1, 1:*n*, *m*:1 y *m*:*n*.

- - > Modelo basado en multiplexores:

- ⇒ Las interconexiones de tipo *m*:1 se implementan conectando un multiplexor *m* a 1 a la entrada del destino.

- ⇒ Las interconexiones de tipo *m:n* se descomponen en n interconexiones de tipo *m:*1.

- Modelo basado en buses:

- ⇒ Tanto las interconexiones de tipo m:1, como las m:n se implementan mediante un bus que conecta todos los destinos y todas las fuentes. Los destinos se conectan al bus directamente y las fuentes a través de un buffer triestado.

- Modelo mixto:

- $\Rightarrow$  Algunas interconexiones se implementan con multiplexores y otras como buses.

- Según el modelo que se elija para el interconexionado el proceso de diseño es diferente.

síntesis arquitectónica y de alto nivel

J.M. Mendias, 20

# otras alternativas de optimización

- - > Que el ciclo de ejecución de las operaciones era inamovible.

- ⇒ Planificación de operaciones.

- > Que toda operación tarda un ciclo en ejecutarse.

- ⇒ Encadenamiento.

- ⇒ Multiciclo.

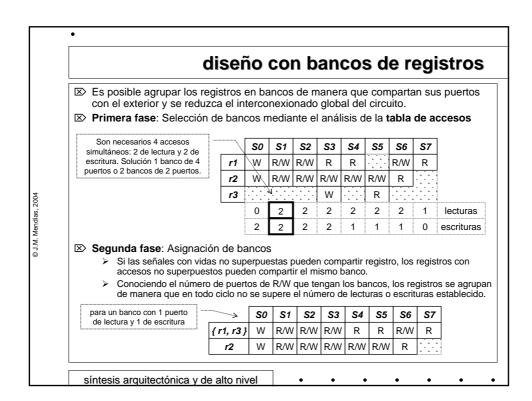

- > Que se deben usar únicamente registros para almacenar señales.

- ⇒ Síntesis con bancos de registros.

- ⇒ Síntesis con memorias RAM.

- ⇒ Otros elementos de almacenamiento: LIFOs, FIFOs, contadores, etc.

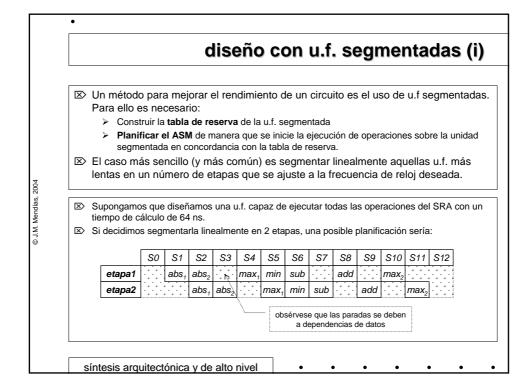

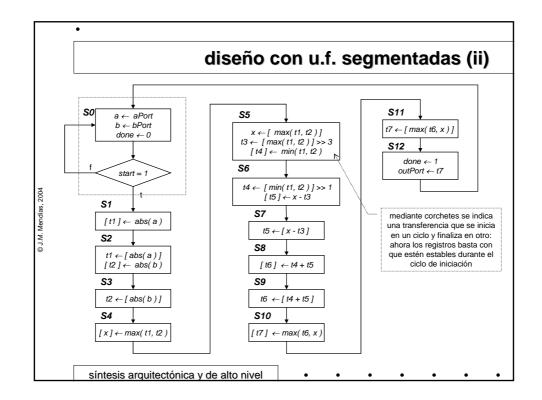

- > Que las unidades funcionales son combinacionales y simples.

- ⇒ Síntesis con unidades segmentadas.

- Otras unidades funcionales: multiplicadores-acumuladores, multiplicadoressumadores, u.f. vectoriales, contadores, etc.

síntesis arquitectónica y de alto nivel

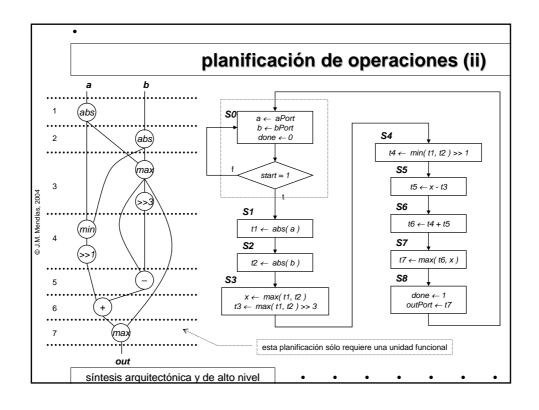

# planificación de operaciones (i)

- Hasta el momento hemos sintetizado partiendo de diagramas ASM en donde las operaciones tenían un ciclo de ejecución asignado.

- El ciclo en que se realiza una operación influencia enormemente los reusos posteriores.

- Sin embargo, dicha planificación fue arbitraria y pueden existir otras mejores.

- Planificación: decide el ciclo en que se ejecuta cada una de las operaciones que componen una computación.

- Toda planificación debe respetar las dependencias de datos, es decir, toda operación debe planificarse en un ciclo igual o posterior al ciclo en que se planifican las operaciones que calculan sus argumentos.

- > Las tareas fundamentales para realizar una planificación son:

- ⇒ Construir un diagrama de flujo de la computación.

- ⇒ Decidir el número de ciclos en que se ejecutará la computación

- ⇒ Asignar a cada operación un ciclo de ejecución según algún criterio de coste.

síntesis arquitectónica y de alto nivel

abs abs abs min max max max out

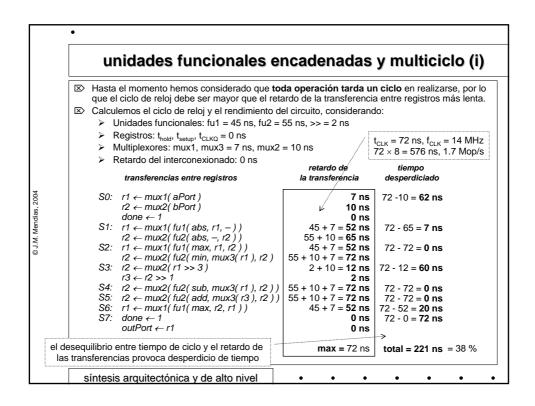

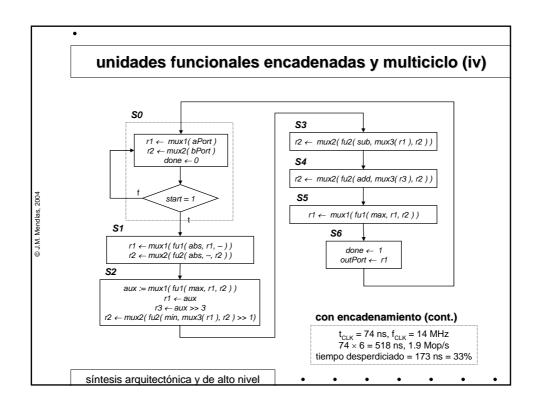

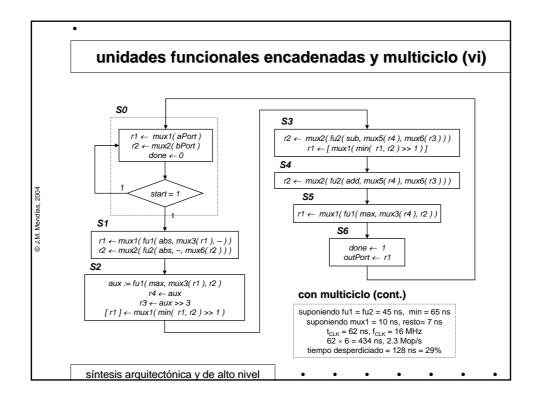

#### unidades funcionales encadenadas y multiciclo (ii)

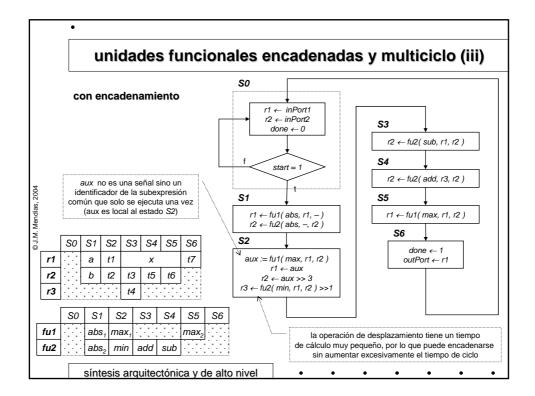

- ☼ Objetivo: reducir el tiempo desperdiciado en cada ciclo, ajustando el tiempo de ciclo y el retardo medio de las transferencias entre registros.

- Encadenamiento: consiste en agrupar la ejecución de varias operaciones con dependencias de datos en un mismo ciclo para aprovechar al máximo el tiempo disponible. Al encadenar operaciones:

- > El número de ciclos requeridos para ejecutar la computación puede disminuir.

- Pueden desaparecen algunos registros intermedios.

- Al concentrarse mayor número de operaciones por ciclo, la reusabilidad del HW puede disminuir

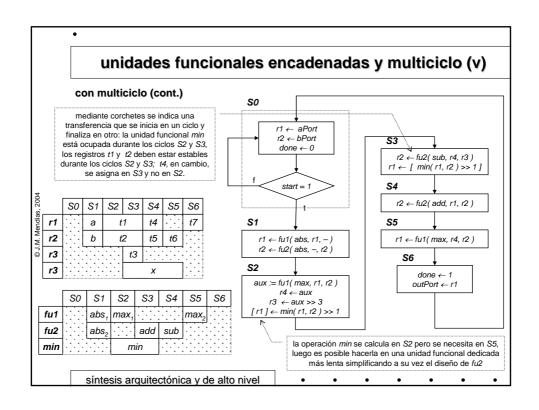

- Multiciclo: consiste en permitir que las operaciones puedan tardar en ejecutarse más de un ciclo, por lo que el tiempo de ciclo no está limitado por la transferencia entre registros más lenta. Al permitir multiciclo:

- > El número de ciclo requeridos para ejecutar la computación puede aumentar.

- La vida de las variables puede aumentar (durante la ejecución de una operación multiciclo los registros fuente deben permanecer estables).

- Al dilatarse por varios ciclos la ejecución de una operación, la reusabilidad del HW puede disminuir.

síntesis arquitectónica y de alto nivel

M. Mendias, 20

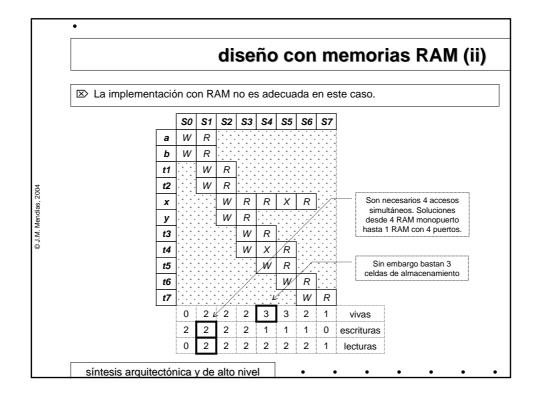

## diseño con memorias RAM (i)

- Cuando existen muchas señales vivas simultáneamente, es conveniente utilizar módulos de memoria en lugar de registros.

- - Mientras los registros tienen un puerto de entrada y otro de salida (por lo que se puede leer y escribir en el mismo ciclo), las memorias tienen típicamente uno o varios puertos bidireccionales (por lo que las lecturas y escrituras deben de hacerse en ciclos diferentes si se hacen a través del mismo puerto).

- > Mientras los registros almacenan un único valor, las memorias almacenan varios.

- Otras de índole tecnológico (señales de control, temporización, etc).

- 🖾 Cuando se diseña con módulos de memoria se necesita concretar:

- El número de módulos de memoria requeridos (función de las características de la memoria: velocidad, número de puertos, etc. y de los accesos a señales).

- El número de celdas de almacenamiento requeridas por módulo (función del número máximo de señales vivas simultáneamente).

- > La asignación de señales a módulos.

- La asignación de señales a celdas de almacenamiento, o lo que es lo mismo, la dirección que ocupará cada señal (para reducir la complejidad de la decodificación).

síntesis arquitectónica y de alto nivel

# J.M. Mendías, 200<sup>2</sup>

#### definición de SAAN

#### Síntesis de alto nivel, algorítmica o arquitectónica

- Entrada: una descripción conductual de nivel algorítmico de una computación y una colección de ligaduras.

- Ligaduras típicas: latencia, tiempo de ciclo, número y tipo de recursos, cadencia de admisión de datos.

- Salida: una ruta de datos (netlist de nivel RT) y una descripción conductual de nivel RT del controlador (secuencia de transferencias entre registros).

- Planificación de operaciones (scheduling): fija el ciclo en que se ejecuta cada una de las operaciones que forman la computación.

- > Selección de recursos (resource binding): determina el número y tipo de recursos funcionales (FUs, regs, mux/buses) requeridos para realizar la computación

- Asignación de recursos (resource allocation): fija el recurso en el que se ejecuta, almacena o transmite cada una de las operaciones y objetos de datos que la forman.

- > Otras tareas: transformación de operaciones, transformación de bucles, segmentación

- Cuando se parte de una de una descripción conductual explícitamente planificada, o de una secuencia de transferencias entre registros sin referencia a recursos, se conoce como síntesis RT.

síntesis arquitectónica y de alto nivel

. . . . . .