### Presentación

Diseño Automático de Sistemas

José Manuel Mendías Cuadros

Dpto. Arquitectura de Computadores y Automática Universidad Complutense de Madrid

## **Profesorado**

### José Manuel Mendías Cuadros

Despacho 3.35 (Facultad de Informática)

o teléfono: 91 394 76 13

o e-mail: mendias@ucm.es

Web: www.dacya.ucm.es/mendias

www.fdi.ucm.es/profesor/mendias (alternativa)

- Tutorías (con solicitud de cita previa por email):

- Lunes, jueves y viernes de 11h a 12h

## Objetivo y metodología

### Objetivo:

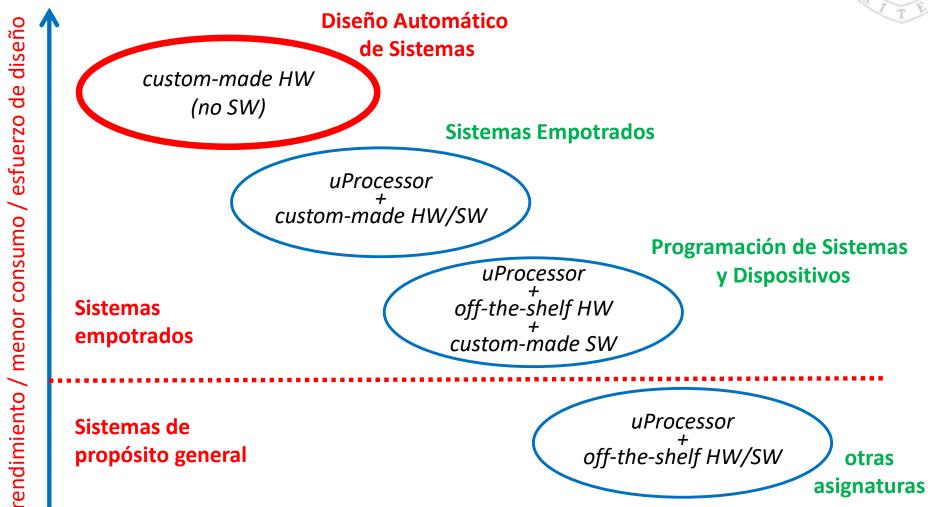

- Capacitar para el diseño VLSI a nivel RT de circuitos integrados de propósito específico (ASIC) mediante su prototipado sobre FPGA.

- Haciendo énfasis:

- Diseño reutilizable a nivel RT (Register-Transfer) basado en VHDL.

- Diseño eficiente a nivel RT sobre FPGA

- Uso de herramientas de diseño automático.

### Metodología:

- Aprender practicando

- Toda la teoría será aplicada en los laboratorios.

- La experiencia facilitará la extrapolación de los conceptos a otros entornos.

- Trabajaremos con una FPGA concreta

- Sin embargo, todo lo aprendido es extrapolable a otras tecnologías VLSI.

### Prerequisitos:

Interés por el diseño hardware.

## Sistemas digitales

alternativas de diseño

## **Contenidos**

- En el curso 2023-24, se actualizó todo el material docente.

- Se ha adaptado a nuevas placas de prototipado y herramientas de diseño.

|   | Tema                                                        | horas |

|---|-------------------------------------------------------------|-------|

| 1 | Diseño automático de sistemas digitales                     | 4     |

| 2 | La placa de prototipado Digilent Basys 3                    | 1     |

| 3 | El entorno de diseño AMD Vivado ML                          | 2     |

| 4 | Especificación de sistemas digitales usando VHDL            | 6     |

| 5 | Especificación usando VHDL'08                               | 1     |

| 6 | Especificación usando Verilog                               | 1     |

|   | Modelos de especificación y diseño (incluidos en prácticas) | 12    |

### **Prácticas:**

- Diseño y prototipado de controladores hardware de dispositivos.

- Diseño y prototipado de sistemas digitales completos.

## Dinámica de clases

- Asistencia obligatoria (mínimo 70%)

- Más de 8 faltas de asistencia => NP en ambas convocatorias.

- Distribución de clases:

- Jueves: Prácticas en laboratorio (50% de las clases) Lab 7

- Viernes: Teoría (50% de las clases) Lab 9 / Aula 5

- Elementos evaluables:

- o Prácticas: 50% de la nota

- Defensa en horario de clase (último día: el último de prácticas en lab)

- La nota aplica a ambas convocatorias (y se conserva de un curso a otro)

- o Proyecto: 50% de la nota

- Se defiende una vez el día del examen

## Dinámica de clases

### **laboratorios**

- Cada estudiante dispondrá de un laboratorio completo en casa:

- Deberá traerlo a clase los días de laboratorio.

- La Facultad prestará el maletín Basys + periféricos durante todo el 1er. cuatrimestre:

- Se recogerá a partir de la fecha indicada por el profesor en la sala de técnicos.

- Se deberá devolver el día de defensa del proyecto.

- Cada estudiante deberá instalarse el entorno de desarrollo:

- Nativamente sobre Windows/Linux, siguiendo las instrucciones del fabricante.

- De ser necesario, el entorno de desarrollo también está instalado en:

- Los laboratorios de la Facultad.

- Los puestos de la biblioteca.

- Los portátiles en préstamo de la Facultad.

# Prácticas valoraciones

|    | Laboratorios                                                                                    | Ptos |

|----|-------------------------------------------------------------------------------------------------|------|

| 1  | Lógica combinacional. Aritmética y acceso a dispositivos elementales de E/S.                    | 0,25 |

| 2  | Lógica secuencial. Lectura de señales asíncronas y módulos genéricos.                           | 0,5  |

| 3  | Máquinas de estados finitos (FSM). Acondicionamiento de las señales de reloj y reset asíncrono. | 0,75 |

| 4  | Validación e instrumentación. Comunicación serie síncrona por un bus PS/2.                      | 0,75 |

| 5  | FSM con ruta de datos. Comunicación con un terminal a través de un bus RS-232.                  | 1    |

| 6  | FSM con flags. Visualización en un monitor VGA.                                                 | 1,25 |

| 7  | Diseños no volátiles. Carga de configuraciones desde una Flash ROM.                             | 0,25 |

| 8  | Diseño con Block RAM. Interfaces alfanuméricos de vídeo.                                        | 1,25 |

| 9  | FSM temporizadas. Interfaces gráficos de vídeo.                                                 | 1,25 |

| 10 | Diseños monociclo vs. multiciclo. Transmisión por bus IIS y procesado en tiempo real de audio.  | 1,5  |

| 11 | Diseño con IP cores. Configuración de una cámara por bus SBBC y captura de vídeo.               | 1,25 |

| 12 | Uso de funciones y procedimientos. Procesado en tiempo real de vídeo (opcional)                 | 1,5  |

Los puntos por prácticas se ponderan por 0.5 en la calificación final

## Distribución de clases

| Enero 2025 |    |    |      |    | Feb | rero 2 | 2025   |       |    |    |    |    |    |  |  |

|------------|----|----|------|----|-----|--------|--------|-------|----|----|----|----|----|--|--|

| 1          | 2  | 3  | 4    | 5  | 6   | 7      |        |       |    |    |    | 1  | 2  |  |  |

| 8          | 9  | 10 | 11   | 12 | 13  | 14     | 3      | 4     | 5  | 6  | 7  | 8  | 9  |  |  |

| 15         | 26 | 17 | 18   | 19 | 20  | 21     | 10     | 11    | 12 | 13 | 8  | 15 | 16 |  |  |

| 20         | 21 | 22 | 23   | 24 | 25  | 26     | 17     | 18    | 19 | 20 | 21 | 22 | 23 |  |  |

| 27         | 28 | 29 | 30   | 31 |     |        | 24     | 25    | 26 | 27 | 28 |    |    |  |  |

| Marzo 2025 |    |    |      |    |     | Abri   | il / M | ayo 2 |    |    |    |    |    |  |  |

|            |    |    |      |    | 1   | 2      |        | 1     | 2  |    | 4  | 5  | 6  |  |  |

| 3          | 4  | 5  | 6    | 7  | 8   | 9      | 7      | 8     | 9  | 10 | 11 | 12 | 13 |  |  |

| 10         | 11 | 12 | 13   | 14 | 15  | 16     | 14     | 15    | 16 | 17 | 18 | 19 | 20 |  |  |

| 17         | 18 | 19 | 20   | 21 | 22  | 23     | 21     | 22    | 23 | 24 | 25 | 26 | 27 |  |  |

| 24         | 25 | 26 | 5(7) | 28 | 29  | 30     | 28     | 29    | 30 | 1  | 2  | 3  | 4  |  |  |

| 31         |    |    |      |    |     |        | 5      | 6     | 7  | 8  | 9  | 10 | 11 |  |  |

Presentación

**DAS**

### DAS

10

## Bibliografía

### Diseño VLSI:

Top-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAs

H. Kaeslin Morgan Kaufmann, 2014

Digital Integrated Circuit Design: From VLSI Architectures to CMOS Fabrication

H. Kaeslin Cambridge University Press, 2008

### Diseño basado en VHDL:

RTL Hardware Design Using VHDL: Coding for Efficiency, Portability, and Scalability

P.P. Chu Cambridge University Press, 2006

FPGA Prototyping by VHDL Examples: Xilinx Spartan-3 Version

P.P. Chu

Wiley, 2008

## Bibliografía

### Diseño Automático:

Synthesis and Optimization of Digital Circuits

G. De Micheli

McGraw Hill, 1994

### Ingeniería VLSI:

- Digital Systems Engineering

W.J. Dally, J.W. Poulton

Cambridge University Press, 2001

- Digital Integrated Circuits: a Design Perspective Jan M. Rabaey, A. Chandrakasan, B. Nikolic Pearson Education International, 2003

12

## Acerca de Creative Commons

- Ofrece algunos derechos a terceras personas bajo ciertas condiciones. Este documento tiene establecidas las siguientes:

- Reconocimiento (Attribution):

En cualquier explotación de la obra autorizada por la licencia hará falta reconocer la autoría.

- No comercial (Non commercial):

La explotación de la obra queda limitada a usos no comerciales.

- Compartir igual (Share alike):

La explotación autorizada incluye la creación de obras derivadas siempre que mantengan la misma licencia al ser divulgadas.

Más información: https://creativecommons.org/licenses/by-nc-sa/4.0/